# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | A Study of High-Speed Direct Digital Frequency Synthesizer Solutions<br>in CMOS Technology                                                                                                   |

| 著者(和文)            | Abdel Martinez Alonso                                                                                                                                                                        |

| Author(English)   | Abdel Martinez Alonso                                                                                                                                                                        |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10892号,<br>授与年月日:2018年3月26日,<br>学位の種別:課程博士,<br>審査員:松澤 昭,岡田 健一,益 一哉,髙木 茂孝,伊藤 浩之,飯塚 哲也,宮原<br>正也                                                         |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10892号,<br>Conferred date:2018/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                         |

| Type(English)     | Doctoral Thesis                                                                                                                                                                              |

## A STUDY OF HIGH-SPEED DIRECT DIGITAL

## **FREQUENCY SYNTHESIZER SOLUTIONS IN CMOS**

## TECHNOLOGY

by

Abdel Martinez Alonso

A Ph.D. dissertation submitted in partial satisfaction of the requirements for the degree of

## **Doctor of Philosophy**

in

**Physical Electronics**

in the

## **Graduate School of Science and Engineering**

of

## **Tokyo Institute of Technology**

Supervised by

Prof. Akira Matsuzawa and Prof. Kenichi Okada

Fall 2017

In memory of my beloved father who shared his faith in future with me.

### ACKNOWLEDGMENT

The time I spent in the Matsuzawa and Okada Laboratory, first as a research student, and then inside the Graduate School of Science and Engineering, has been a challenging and enriching journey. During these years, I have got hands-on experience in the design flow of mixed-signal integrated circuits (IC) as part of a top-class and multicultural research group. Completion of this doctoral dissertation wouldn't have been possible without the support of several people. I would like to express my sincere gratitude to all of them.

First of all, I am deeply indebted to my advisor Prof. Akira Matsuzawa for all his support throughout the course of the study. His brilliant career and dedication to science are a source of constant inspiration. Thank you very much for the privilege of receiving your invaluable guidance. Prof. Matsuzawa has always made himself available to clarify any doubts and share his intuition, knowledge, and experience in the field of IC design. His advice, on both research as well as on my career, have been priceless.

I also express appreciation to my associated advisor, Prof. Kenichi Okada, for his counsel and insights during the various phases of my graduate student life. His constructive evaluation of my work helped me to give my best.

I sincerely thank assistant professor, Prof. Masaya Miyahara, for his support throughout my research. This study has been benefited from his always useful reviews, comments and suggestions.

I extend my acknowledgments to Prof. Noboru Ishihara for his always kind advice and valuable time during our interviews as part of the Mentor Program.

I would also like to show my gratitude to the Ph.D. committee members, Prof. Kazuya Masu, Prof. Shigetaka Takagi, Prof. Hiroyuki Ito, and Prof. Tetsuya Iizuka for taking the time out of their busy schedule to examine my dissertation.

I am very grateful to the secretaries, Yoshino Kasuga and Makiko Tsunashima for they constant support and attention to every detail. I would also like to thank Japanese Ministry of Education, Culture, Sports, Science and Technology (MEXT) for its financial support.

Personally, I would like to praise all my friends in the lab, who have supported me academically and personally, making this graduate program an unforgettable stage of my life. I would like to thank Dr. Zule Xu for his help with my research in its early stages. I am especially thankful to Anugerah Firdauzi for our brainstorming sessions and valuable feedbacks. My sincere gratitude also goes to my colleagues from the Research & Development Telecommunications Institute, Lacetel. In the last few years, I have formed several productive collaborations and wonderful friendships, which I am sure will last for long periods to come.

Lastly, I would like to thank my mother, wife, family and friends for their support to make all of this possible.

### ABSTRACT

This dissertation describes the trends and limitations of the direct digital frequency synthesizer (DDFS) technology and the design methodology aimed to maximize the throughput in CMOS-based DDFSs. High-speed architectures for a phase accumulator, a phase to amplitude converter, and a two-times interleaved resistive digital to analog converter featuring a random swapping thermometer coding dynamic element matching core are discussed. Solutions for high-speed digital modulations are also integrated. Three proof-of-concept chips confirm the merits of the proposed approach. To begin, a 2GS/s synthesizer consuming only 59mW/(GS/s) is reported. The first CMOS-based DDFS achieving a 7GS/s operation is also characterized. Finally, the only DDFS solution supporting 7GS/s and featuring frequency, phase and amplitude modulations is demonstrated. The potential applications of these developments are also discussed.

## TABLE OF CONTENTS

| Acknowledg    | gmentiii                                                              |

|---------------|-----------------------------------------------------------------------|

| Abstract      |                                                                       |

| Table of Cor  | ntentsvii                                                             |

| List of Figur | resix                                                                 |

| List of Table | S XV                                                                  |

| Chapter 1:    |                                                                       |

| Trends and 1  | imitations of the direct digital frequency synthesis technology 1     |

| 1.1           | Overview of high-speed DDFS architectures                             |

| 1.2           | Non-idealities in DM-DDFS solutions                                   |

| 1.3           | State of the art                                                      |

| 1.4           | DDFS applications in radar technology11                               |

| 1.5           | Future evolution of DDFS applications                                 |

| 1.6           | Design challenges of high-speed DDFS solutions in CMOS technology. 19 |

| 1.7           | Organization of the dissertation                                      |

| Chapter 2:    |                                                                       |

| Design meth   | odology for high-speed CMOS-based DM-DDFS                             |

| 2.1           | Sequencing methods                                                    |

| 2.2           | Latch-based digital design                                            |

| 2.3           | Interleaved digital to analog converter                               |

| 2.4           | High-speed CMOS-friendly two-times interleaved RDAC                   |

| 2.5           | Dynamic element matching techniques                                   |

| 2.6           | Summary of the design methodology for high-speed CMOS-based           |

| DM-DI         | DFS                                                                   |

| Chapter 3:    |                                                                       |

| Complement    | tary dual-phase latch-based NCO                                       |

| 3.1           | 24-bits complementary dual-phase latch-based phase accumulator        |

| 3.2           | Dual-phase sum of product terms based phase to amplitude converter 45 |

| 3.3           | System implementation                                                 |

| 3.4           | Design verification                                                   |

| 3.5           | Performance comparison                                                |

| 3.6           | Summary of the complementary dual-phase latch-based NCO 55            |

| Chapter 4:    |                                                                       |

| Two-times in  | nterleaved RDAC                                                       |

| 4.1           | High-speed architecture for random swapping thermometer coding        |

| dynamic element matching                     |                                     |

|----------------------------------------------|-------------------------------------|

| 4.2 RDAC cell                                |                                     |

| 4.3 Hybrid clock distribution network        |                                     |

| 4.4 Static timing analysis                   |                                     |

| 4.5 Mixed-signal layout consideration        | s                                   |

| 4.6 Design verification                      |                                     |

| 4.7 Summary of the two-times interlea        | ved RDAC74                          |

| Chapter 5:                                   |                                     |

| Solutions for high-speed digital modulations |                                     |

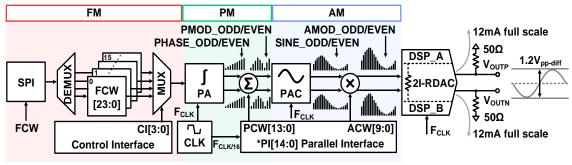

| 5.1 High-speed phase-adder                   |                                     |

| 5.2 High-speed amplitude-multiplier          |                                     |

| 5.3 Design verification                      |                                     |

| 5.4 Summary of the solutions for high        | -speed digital modulations          |

| Chapter 6:                                   |                                     |

| Proof-of-concept chips                       |                                     |

| 6.1 A 2GS/s 118mW DM-DDFS in 65              | nm CMOS technology                  |

| 6.2 A 7GS/s DM-DDFS with a two-ti            | mes interleaved RDAC in 65nm CMOS   |

| technology                                   |                                     |

| 6.3 A High-speed DDFS MMIC v                 | with frequency, phase and amplitude |

| modulations in 65nm CMOS technology          |                                     |

| 6.4 Summary of the proof-of-concept          | chips114                            |

| Chapter 7:                                   |                                     |

| Conclusions and future work                  |                                     |

| 7.1 Academic perspective                     |                                     |

| 7.2 Industrial perspective                   |                                     |

| 7.3 Application-specific perspective         |                                     |

| 7.4 Future work                              |                                     |

| References                                   |                                     |

| Appendix A: Publication list                 |                                     |

## LIST OF FIGURES

| Fig. 1.1. Conventional DM-DDFS architecture.                                   | 1             |

|--------------------------------------------------------------------------------|---------------|

| Fig. 1.2. High-speed DDFS architectures. a) AM-DDFS. b) NLD-DDFS. c)           |               |

| Fig. 1.3. Model of a non-ideal DM-DDFS.                                        |               |

| Fig. 1.4. DDFS phase noise model                                               | 6             |

| Fig. 1.5. DDFS quantization noise floor                                        | 7             |

| Fig. 1.6. Complete-DDFS-solutions performance                                  | 9             |

| Fig. 1.7. W-SFDR performance of commercially available complete-DDFS           | -solutions.10 |

| Fig. 1.8. PE performance of commercially available complete-DDFS-solution      | ons11         |

| Fig. 1.9. Generated and received chirp signals. a) Frequency domain. b) T      | ime domain.   |

|                                                                                | 12            |

| Fig. 1.10. VCO-based FMCW radar transmitter.                                   | 13            |

| Fig. 1.11. DDFS-PLL hybrid FMCW radar transmitter.                             | 13            |

| Fig. 1.12. FPGA+RF-DAC based FMCW radar transmitter.                           | 14            |

| Fig. 1.13. DRO+DDFS based FMCW radar transmitter.                              | 15            |

| Fig. 1.14. Components of the onboard sense-and-avoid system                    | 16            |

| Fig. 1.15. DTV broadcasting systems allocation and evolution                   | 17            |

| Fig. 1.16. Direct polar modulator architecture.                                | 18            |

| Fig. 1.17. SFDR requirement of systems allocated in the VHF, UHF, L and        | d S bands up  |

| to 2.7GHz                                                                      | 18            |

| Fig. 1.18. Organization of the dissertation.                                   | 22            |

| Fig. 2.1. DM-DDFS implementations in compound semiconductor technology         | ogies23       |

| Fig. 2.2. Area and energy associated with different pins of flip-flop and late | ch cells. Low |

| threshold voltage (LVT), 65nm CMOS standard cell library                       | 26            |

| Fig. 2.3. Two-phase transparent latches sequencing method                      | 27            |

| Fig. 2.4. Complementary dual-phase latch-based sequencing method               |               |

| Fig. 2.5. Conventional interleaved DAC architecture.                           | 29            |

| Fig. 2.6. Gain mismatch error profiles.                                        | 30            |

| Fig. 2.7. Duty cycle error profiles.                                           | 30            |

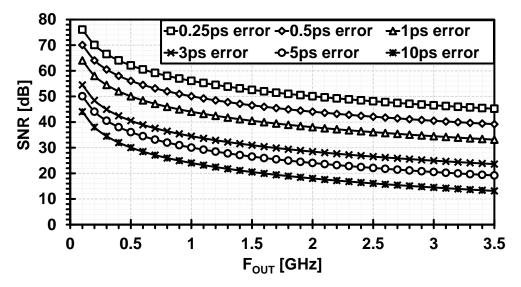

| Fig. 2.8. SNR degradation due to clock jitter.                                 |               |

| Fig. 2.9. General architecture of the proposed interleaved RDAC.               |               |

| Fig. 2.10. High-speed design methodology for CMOS-based DDFS                   | 34            |

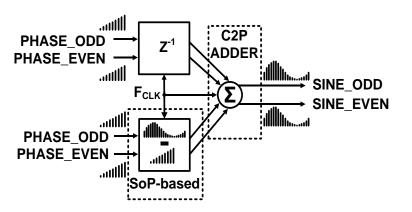

| Fig. 3.1. Proposed NCO general architecture and timing diagram.                |               |

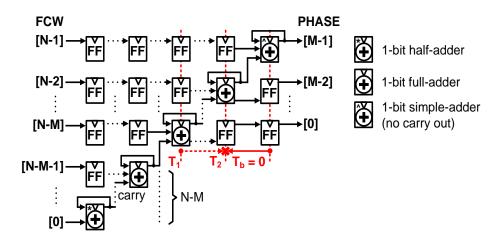

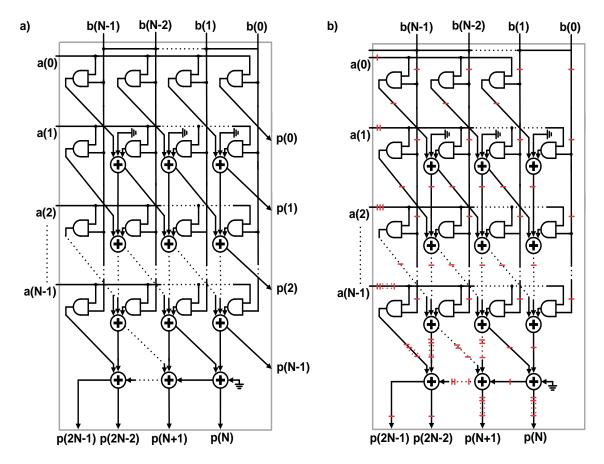

| Fig. 3.2. Conventional pipelined phase accumulator                             |               |

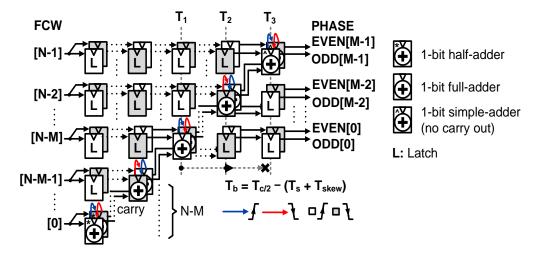

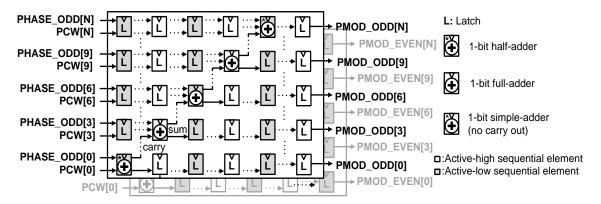

| Fig. 3.3. Complementary dual-phase latch-based phase accumulator                       |

|----------------------------------------------------------------------------------------|

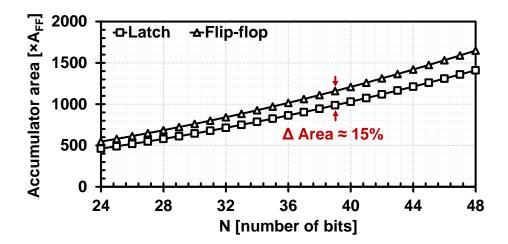

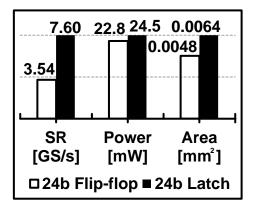

| Fig. 3.4. Normalized area vs. accumulator size40                                       |

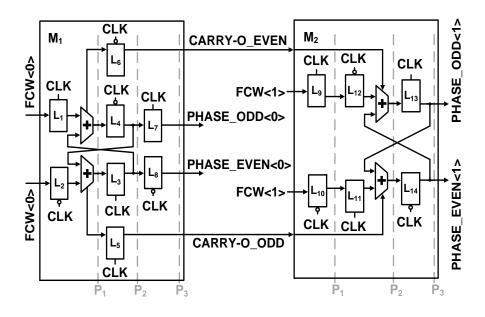

| Fig. 3.5. 2-bits complementary dual-phase latch-based phase accumulator41              |

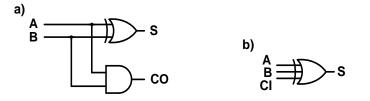

| Fig. 3.6. Half-adder and simple-adder circuits                                         |

| Fig. 3.7. Full-adder circuit42                                                         |

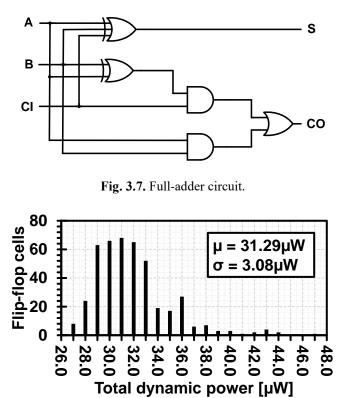

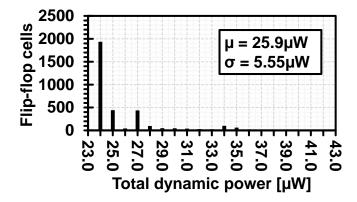

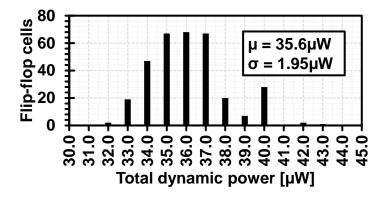

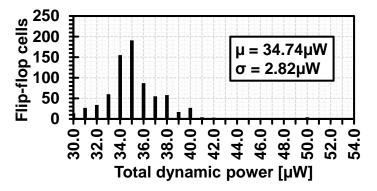

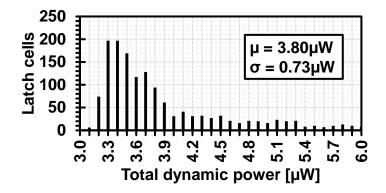

| Fig. 3.8. 24-bits flip-flop based phase accumulator. Dynamic power distribution of     |

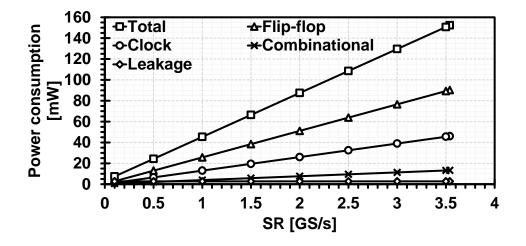

| individual registers when running at 3.54GS/s42                                        |

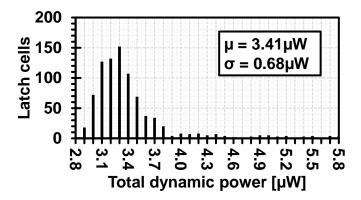

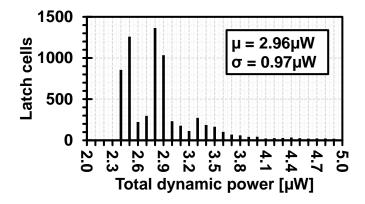

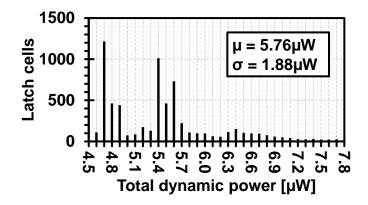

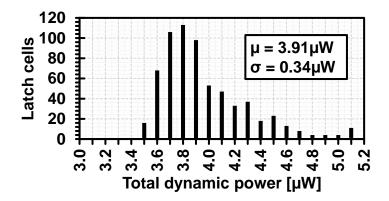

| Fig. 3.9. 24-bits complementary dual-phase latch-based phase accumulator. Dynamic      |

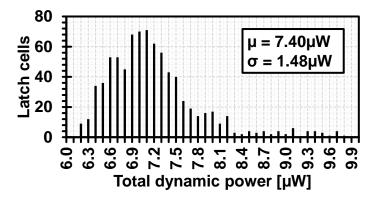

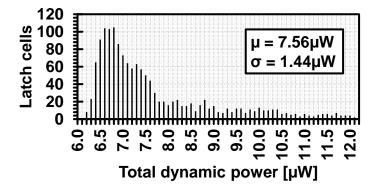

| power distribution of individual registers when running at 3.54GS/s43                  |

| Fig. 3.10. 24-bits complementary dual-phase latch-based phase accumulator. Dynamic     |

| power distribution of individual registers when running at 7.6GS/s43                   |

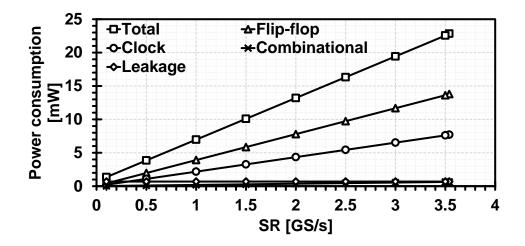

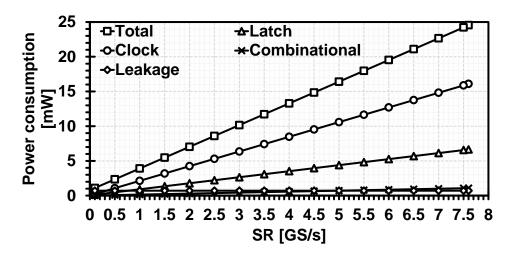

| Fig. 3.11. Power breakdown. 24-bits accumulator. Flip-flop based architecture.         |

| 3.54GS/s                                                                               |

| Fig. 3.12. Power breakdown. 24-bits accumulator. Latch-based architecture. 7.6GS/s44   |

| Fig. 3.13. Post layout simulation results                                              |

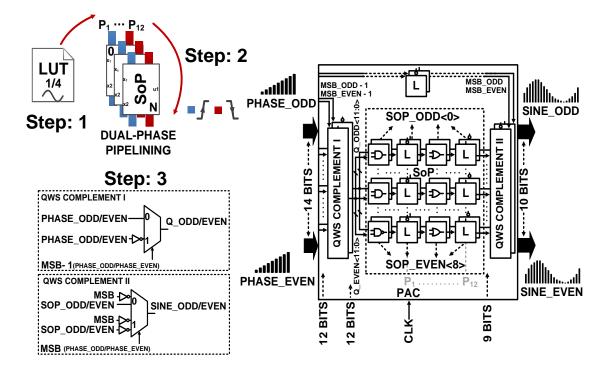

| Fig. 3.14. SoP-PAC technique design flow                                               |

| Fig. 3.15. Quarter wave symmetry technique46                                           |

| Fig. 3.16. Flip-flop based SoP-PAC. Dynamic power distribution of individual registers |

| when running at 3.54GS/s47                                                             |

| Fig. 3.17. Latch-based SoP-PAC. Dynamic power distribution of individual registers     |

| when running at 3.54GS/s47                                                             |

| Fig. 3.18. Latch-based SoP-PAC. Dynamic power distribution of individual registers     |

| when running at 6.92GS/s48                                                             |

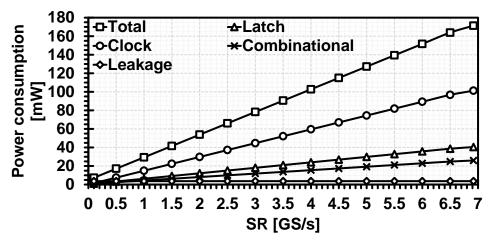

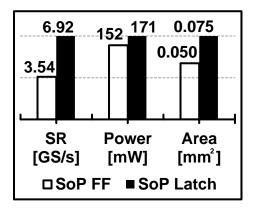

| Fig. 3.19. Power breakdown. SoP-PAC. Flip-flop based architecture. 3.54GS/s48          |

| Fig. 3.20. Power breakdown. SoP-PAC. Latch-based architecture. 6.92GS/s                |

| Fig. 3.21. Post layout simulation results. PAC block                                   |

| Fig. 3.22. Floorplan view of the proposed NCO                                          |

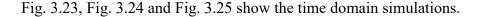

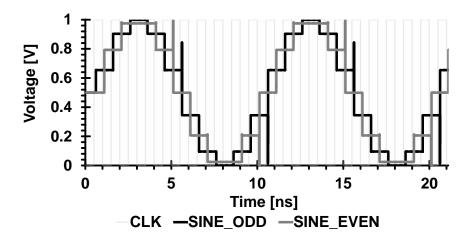

| Fig. 3.23. Behavioral simulation. $F_{CLK} = 3.4$ GHz. $F_{OUT} = 340$ MHz             |

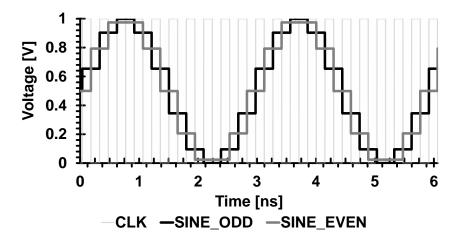

| Fig. 3.24. Post-synthesis simulation. $F_{CLK} = 1$ GHz. $F_{OUT} = 100$ MHz           |

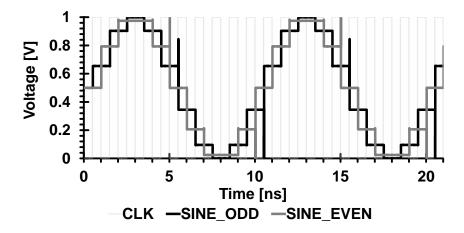

| Fig. 3.25. Post-layout simulation. $F_{CLK}$ = 1GHz. $F_{OUT}$ = 100MHz                |

| Fig. 3.26. Transient simulation. $F_{CLK}$ = 3.4GHz. $F_{OUT}$ = 340MHz                |

| Fig. 3.27. Worst case SFDR. $F_{CLK}$ = 3.4GHz. $F_{OUT}$ = 2.26GHz                    |

| Fig. 3.28. SFDR vs DDFS output frequency. $F_{CLK}$ = 3.4GHz                           |

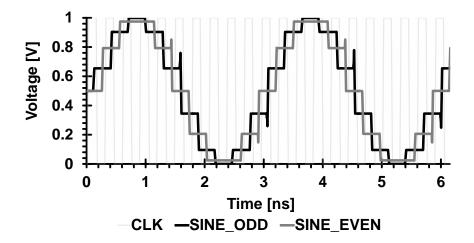

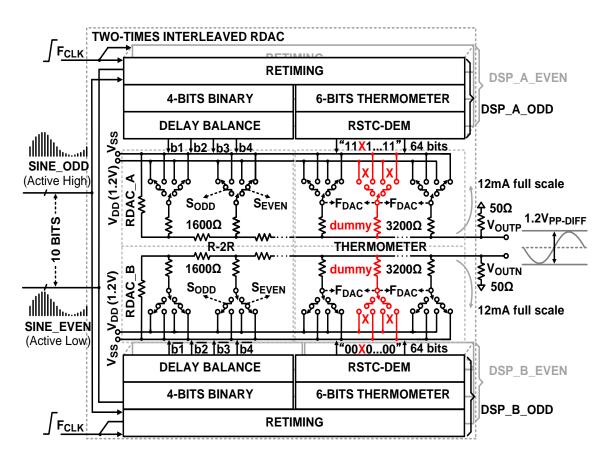

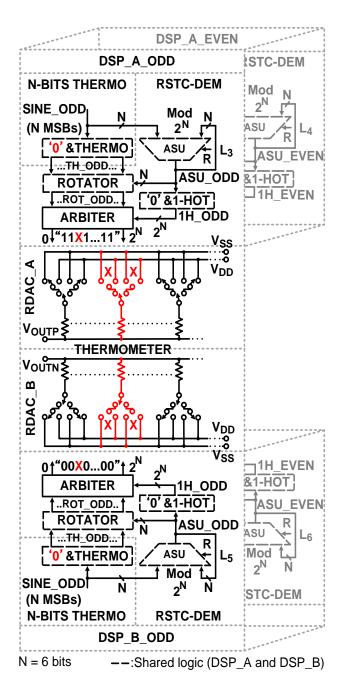

| Fig. 4.1. Two-times interleaved RDAC architecture                                      |

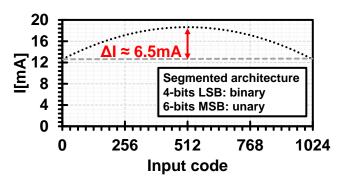

| Fig. 4.2. Code dependent current drawn from the power supply                           |

| Fig. 4.3. Conventional N-bit RSTC-DEM encoder                                          |

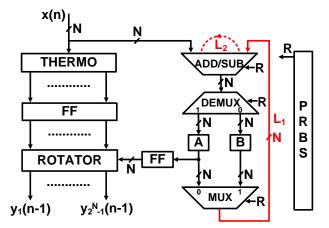

| Fig. 4.4. Proposed N-bit high-speed RSTC-DEM encoder                                                | 0 |

|-----------------------------------------------------------------------------------------------------|---|

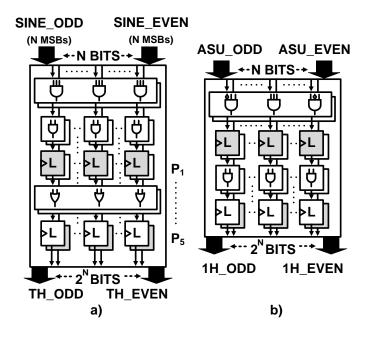

| Fig. 4.5. High-speed encoders. a) Binary-to-thermometer. b) one-hot encoders                        | 1 |

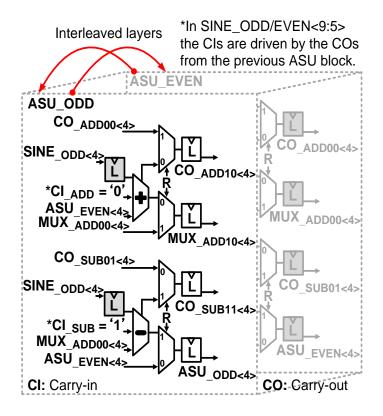

| Fig. 4.6. Complementary dual-phase latch-based ASU                                                  | 1 |

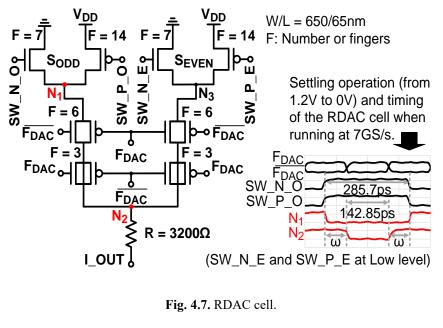

| Fig. 4.7. RDAC cell                                                                                 | 3 |

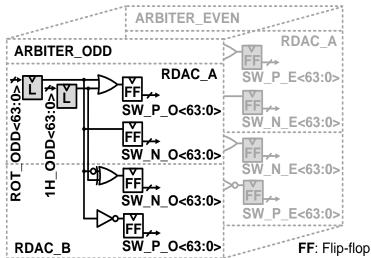

| Fig. 4.8. ARBITER circuit                                                                           | 3 |

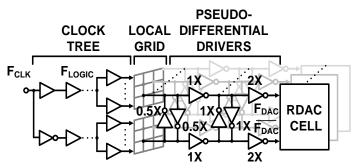

| Fig. 4.9. Hybrid clock distribution network                                                         | 5 |

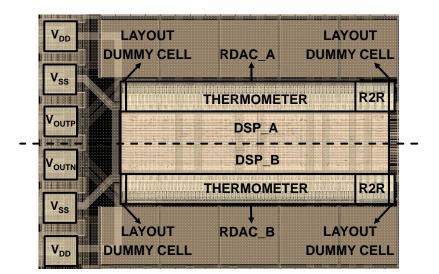

| Fig. 4.10. RDAC layout view                                                                         | 8 |

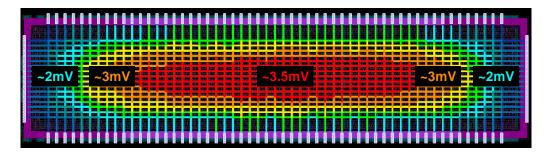

| Fig. 4.11. Digital V <sub>DD</sub> . IR drop in the synthesized power network                       | 8 |

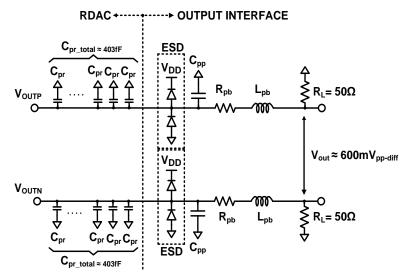

| Fig. 4.12. Output interface simulation model                                                        | 9 |

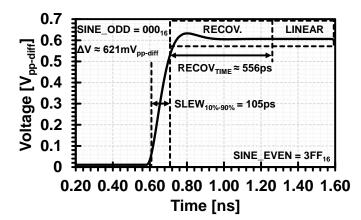

| Fig. 4.13. Simulation of the settling time zones                                                    | 0 |

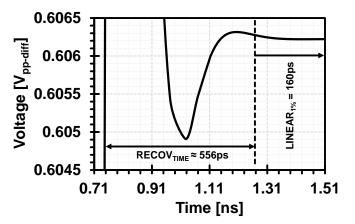

| Fig. 4.14. Magnified recovery and linear zones                                                      | 0 |

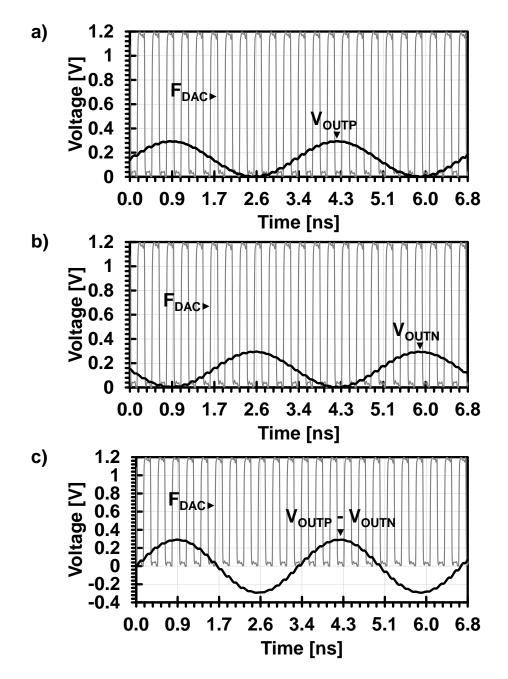

| Fig. 4.15. Transistor level simulation. $F_{CLK} = 6.8$ GHz. $F_{OUT} = 299.96$ MHz. a) $V_{OUT}$   | P |

| waveform. b) V <sub>OUTN</sub> waveform. c) Differential output waveform7                           | 1 |

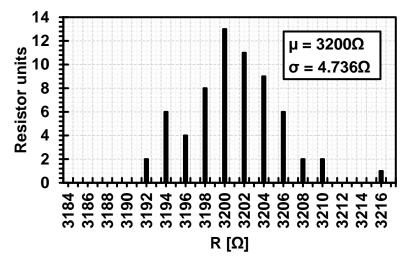

| Fig. 4.16. Resistor mismatch model                                                                  | 2 |

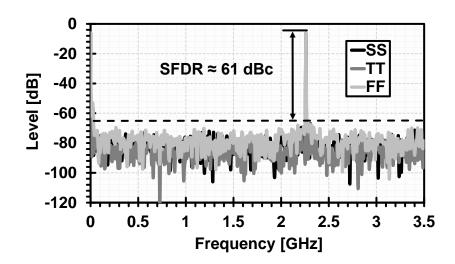

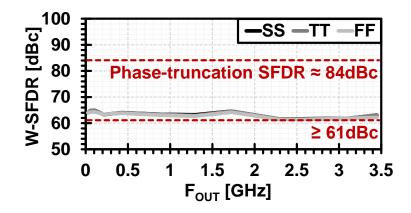

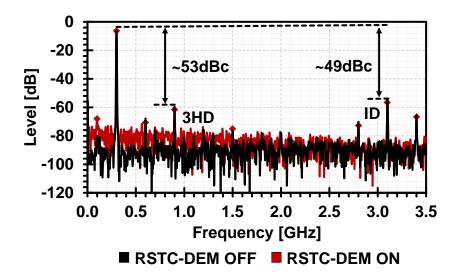

| Fig. 4.17. W-SFDR. <i>F</i> <sub>CLK</sub> = 3.4GHz. <i>F</i> <sub>OUT</sub> = 299.96MHz7           | 3 |

| Fig. 4.18. W-SFDR. <i>F</i> <sub>CLK</sub> = 3.4GHz. <i>F</i> <sub>OUT</sub> = 2.699GHz7            | 3 |

| Fig. 4.19. W-SFDR vs DDFS output frequency. $F_{CLK}$ = 3.4GHz                                      | 4 |

| Fig. 5.1. Complete-DDFS-solution architecture featuring FM, PM and AM modulation                    | S |

| in the digital domain                                                                               |   |

| Fig. 5.2. N-bits flip-flop based pipelined adder                                                    | 7 |

| Fig. 5.3. <i>N</i> -bits complementary dual-phase latch-based pipeline adder                        | 7 |

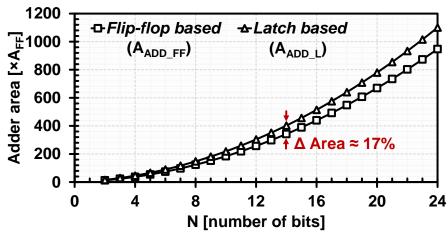

| Fig. 5.4. Estimated areas of different pipelined adder circuits                                     | 9 |

| Fig. 5.5. 14-bits flip-flop based adder. Dynamic power distribution of individua                    |   |

| registers when running at 4GS/s                                                                     | 9 |

| Fig. 5.6. 14-bits complementary dual-phase latch-based adder. Dynamic power                         | r |

| distribution of individual registers when running at 4GS/s79                                        | 9 |

| Fig. 5.7. 14-bits complementary dual-phase latch-based adder. Dynamic power                         | r |

| distribution of individual registers when running at 8GS/s                                          | 0 |

| Fig. 5.8. Power breakdown. 14-bits flip-flop based pipelined adder implemented in                   | n |

| 65nm CMOS standard cell technology                                                                  | 0 |

| Fig. 5.9. Power breakdown. 14-bits complementary dual-phase latch-based pipeline                    | d |

| adder implemented in 65nm CMOS standard cell technology8                                            | 0 |

| Fig. 5.10. Post layout simulation results                                                           | 1 |

| Fig. 5.11. Parallel multiplier architectures. a) $2 \times N$ -bits precision. Non-pipelined. b     |   |

| <i>N</i> -bits precision pipelined8                                                                 | 2 |

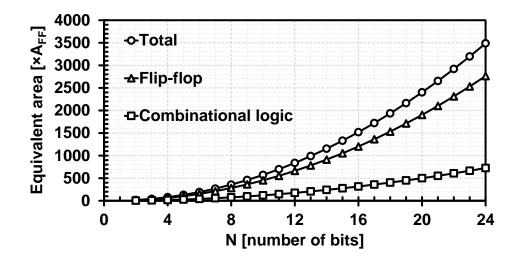

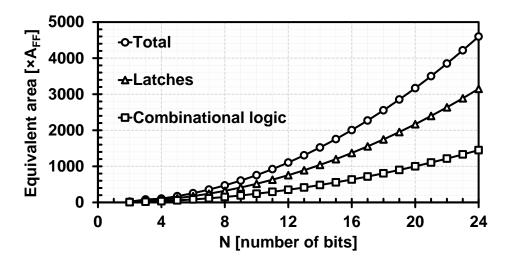

| Fig. 5.12. Equivalent area of different $N \times N$ half-resolution parallel multipliers. Flip-flo | р |

| based pipelining                                                                 |             |

|----------------------------------------------------------------------------------|-------------|

| Fig. 5.13. Equivalent area of different $N \times N$ half-resolution parallel mu | ultipliers. |

| Latch-based pipelining                                                           |             |

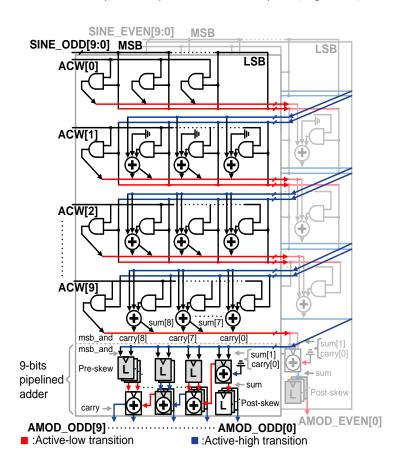

| Fig. 5.14. 10×10-bits parallel multiplier employing the complementary d          | ual-phase   |

| latch-based method.                                                              |             |

| Fig. 5.15. Dynamic power consumption of the register cells in a 10               | )×10-bits   |

| half-resolution multiplier. Flip-flop based pipelined architecture. SR=          | 3.98GS/s    |

|                                                                                  | 85          |

| Fig. 5.16. Dynamic power consumption of the register cells in a 10               | )×10-bits   |

| half-resolution multiplier. Latch-based pipelined architecture. $SR=3.9$         | 8GS/s.86    |

| Fig. 5.17. Dynamic power consumption of the register cells in a 10               | )×10-bits   |

| half-resolution multiplier. Latch-based pipelined architecture. SR=7.87          | 7GS/s86     |

| Fig. 5.18. Power breakdown. 10-bits half-resolution parallel multiplier. Flip-f  | lop based   |

| architecture                                                                     |             |

| Fig. 5.19. Power breakdown. 10-bits half-resolution parallel multiplier. La      | tch-based   |

| architecture                                                                     |             |

| Fig. 5.20. Post-layout simulation results.                                       |             |

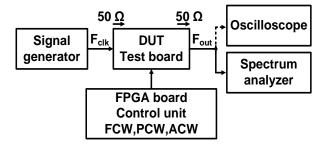

| Fig. 5.21. $F_{OUT} = 99.92$ MHz. Output carrier being OOK modulated at 6.8GS/s. | 88          |

| Fig. 5.22. $F_{OUT} = 99.92$ MHz. Output carrier being BPSK modulated at 6.8GS/s | 88          |

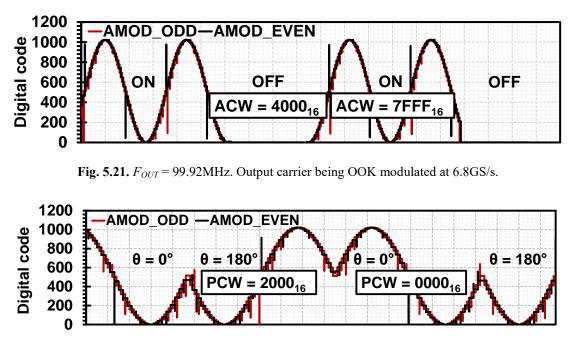

| Fig. 6.1. Measurement setup                                                      | 90          |

| Fig. 6.2. 2GS/s DM-DDFS block diagram.                                           | 91          |

| Fig. 6.3. Voltage-mode RDAC.                                                     | 91          |

| Fig. 6.4. Die micrograph. 2GS/s solution                                         |             |

| Fig. 6.5. W-SFDR vs DM-DDFS output frequency.                                    |             |

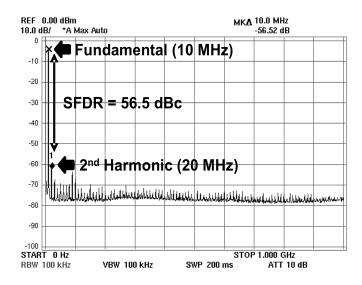

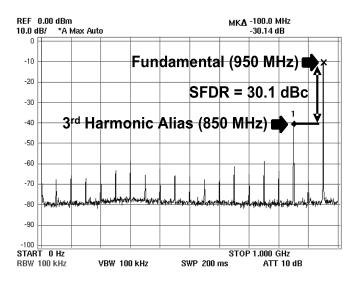

| Fig. 6.6. Best case W-SFDR. $F_{CLK} = 1$ GHz. $SR = 2$ GS/s                     |             |

| Fig. 6.7. Worst case W-SFDR. $F_{CLK} = 1$ GHz. $SR = 2$ GS/s                    |             |

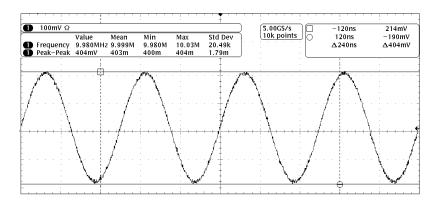

| Fig. 6.8. DM-DDFS output waveform. $F_{OUT}$ = 10MHz. $SR$ = 2GS/s               | 94          |

| Fig. 6.9. DM-DDFS output waveform. $F_{OUT}$ = 950MHz. $SR$ = 2GS/s              | 94          |

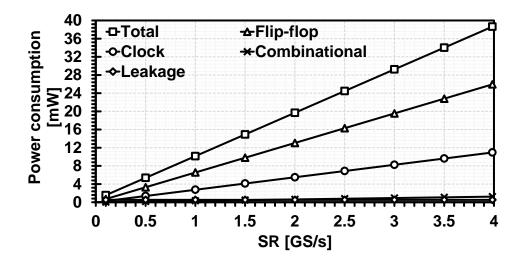

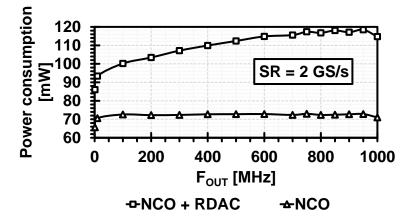

| Fig. 6.10. Power consumption vs. DM-DDFS output frequency.                       | 94          |

| Fig. 6.11. Power efficiency vs. sampling rate                                    | 96          |

| Fig. 6.12. 7GS/s complete-DDFS-solution                                          | 96          |

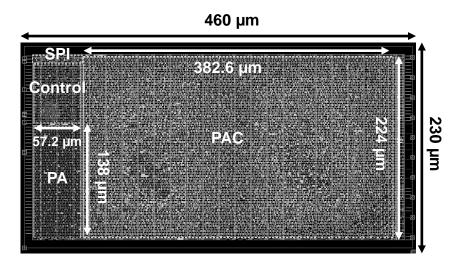

| Fig. 6.13. Die micrograph. 7GS/s DM-DDFS solution                                |             |

| Fig. 6.14. Evaluation board.                                                     |             |

| Fig. 6.15. W-SFDR and output waveform. $F_{OUT}$ = 102.8MHz. $SR$ = 7GS/s        |             |

| Fig. 6.16. W-SFDR and output waveform. $F_{OUT}$ = 3.499GHz. $SR$ = 7GS/s        |             |

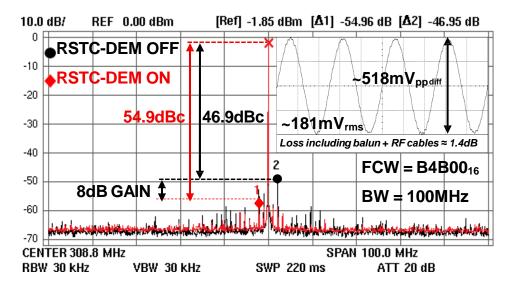

| Fig. 6.17. N-SFDR and output waveform. $F_{OUT}$ = 308.8MHz. $SR$ = 7GS/s        |             |

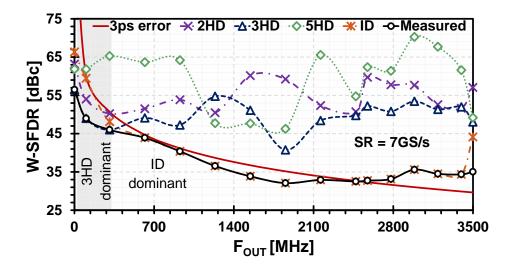

| Fig. 6.18. Measured W-SFDR vs DM-DDFS output frequency                                         |

|------------------------------------------------------------------------------------------------|

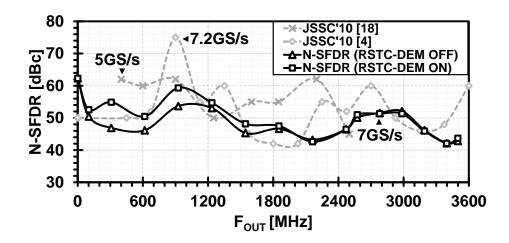

| Fig. 6.19. Measured N-SFDR vs DM-DDFS output frequency101                                      |

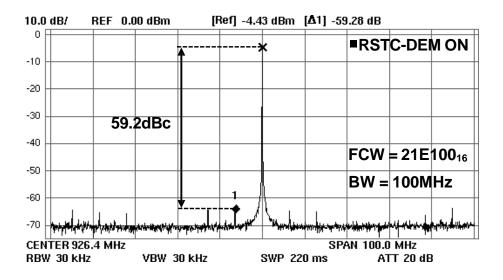

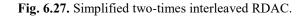

| Fig. 6.20. N-SFDR sweet-spot. $F_{OUT}$ = 926.4MHz. $SR$ = 7GS/s101                            |

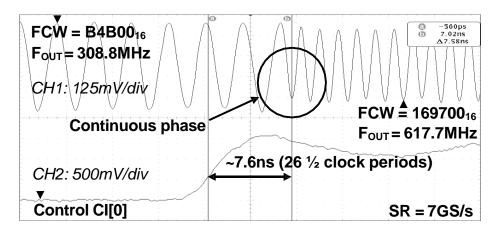

| Fig. 6.21. System latency101                                                                   |

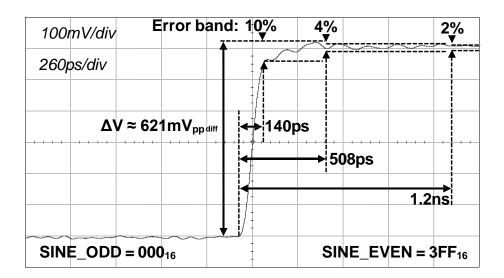

| Fig. 6.22. Full-scale settling time                                                            |

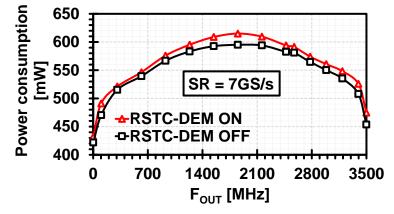

| Fig. 6.23. Power consumption vs DM-DDFS output frequency                                       |

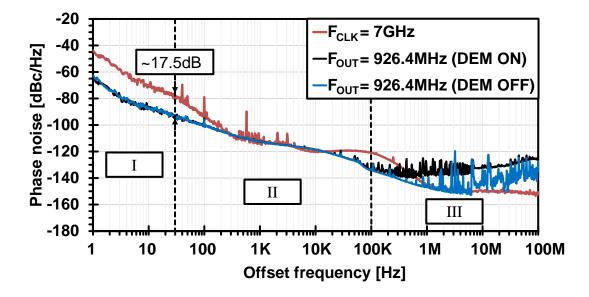

| Fig. 6.24. Absolute phase noise at $F_{OUT} = 926.4$ MHz                                       |

| Fig. 6.25. W-SFDR vs. sampling rate                                                            |

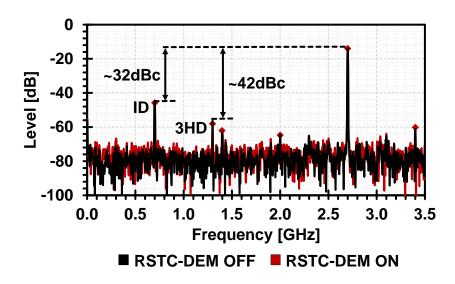

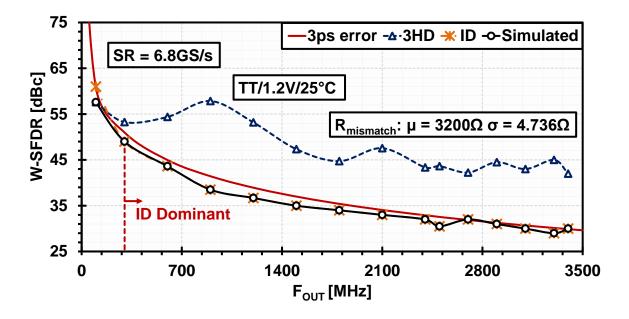

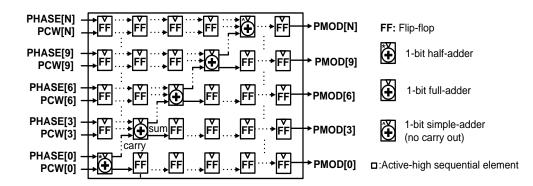

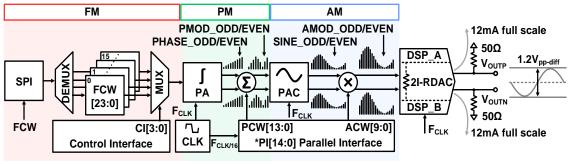

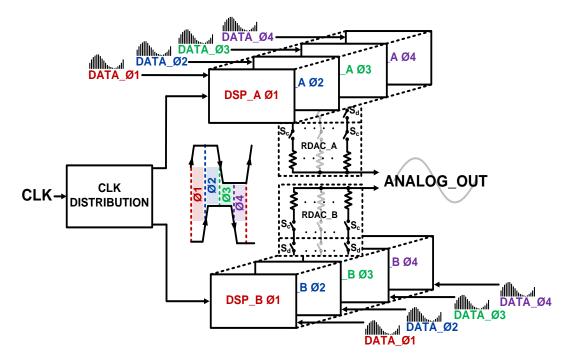

| Fig. 6.26. 7GS/s complete-DDFS-solution featuring FM, PM and AM capabilities106                |

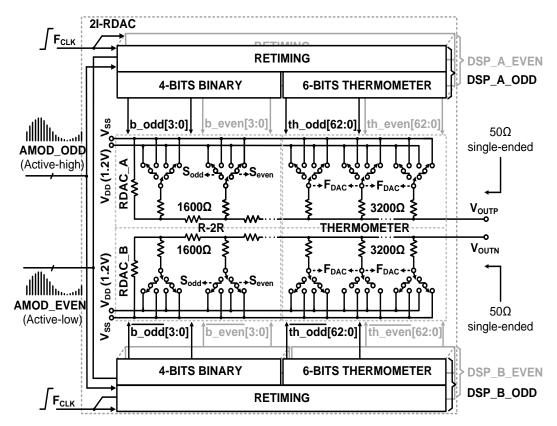

| Fig. 6.27. Simplified two-times interleaved RDAC106                                            |

| Fig. 6.28. Die micrograph. 7GS/s + FM/PM/AM DM-DDFS solution107                                |

| Fig. 6.29. N-SFDR at $F_{OUT}$ = 926.4MHz. $SR$ = 7GS/s                                        |

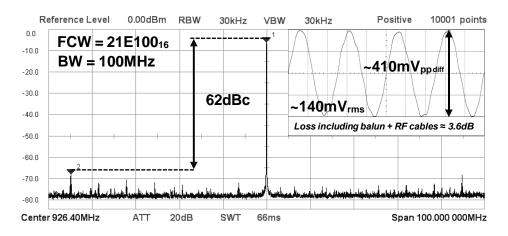

| Fig. 6.30. System latency                                                                      |

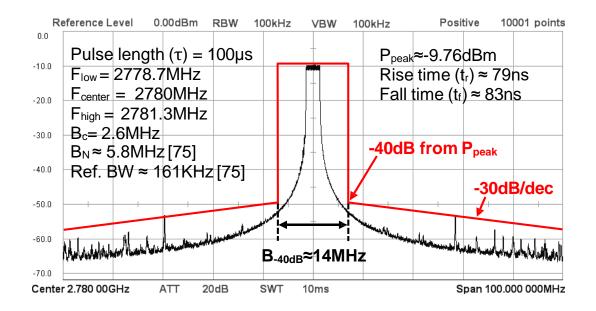

| Fig. 6.31. LFM spectrum and OoB mask. $SR = 7GS/s$                                             |

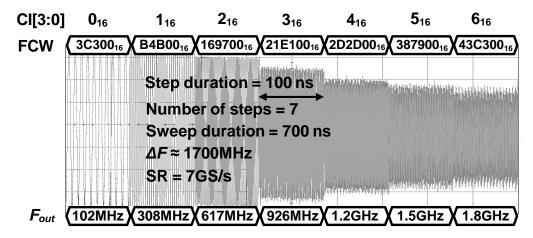

| Fig. 6.32. Wide-band frequency sweep among 7 pre-stored FCW registers                          |

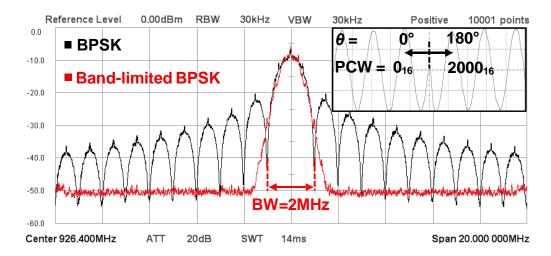

| Fig. 6.33. 1Mbps BPSK modulated signal. Spectra and time domain waveform. $F_{carrier} =$      |

| 926.4MHz. <i>SR</i> = 7GS/s110                                                                 |

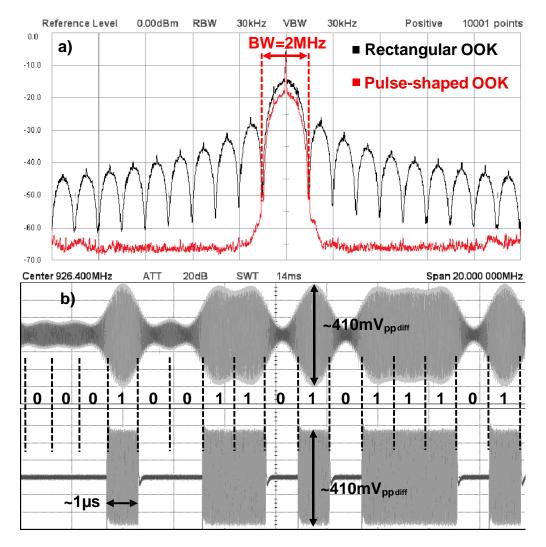

| Fig. 6.34. 1Mbps OOK modulated signal. Spectra (a) and waveforms (b) with and                  |

| without Gaussian pulse-shaping. <i>F<sub>carrier</sub></i> = 926.4MHz. <i>SR</i> = 7GS/s111    |

| Fig. 6.35. Measured absolute phase noise                                                       |

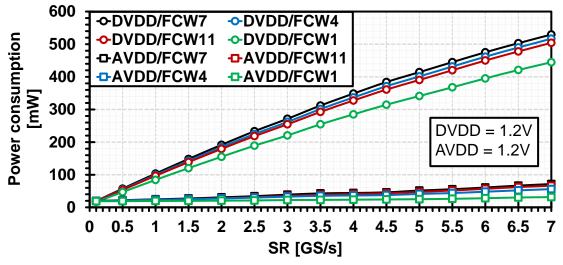

| Fig. 6.36. Power consumption vs. sampling rate113                                              |

| Fig. 6.37. W-SFDR vs. sampling rate114                                                         |

| Fig. 7.1. Conventional and proposed design approach for high-speed                             |

| complete-DDFS-solutions in CMOS technology118                                                  |

| Fig. 7.2. Comparison with commercially available complete-DDFS-solutions.                      |

| W-SFDR vs. sampling rate118                                                                    |

| Fig. 7.3. Comparison with commercially available complete-DDFS-solutions. Power                |

| efficiency vs. sampling rate119                                                                |

| Fig. 7.4. Measured N-SFDR performance vs. required SFDR120                                     |

| Fig. 7.5. Progress history of this work and target area121                                     |

| Fig. 7.6. 2015 ITRS logic core device technology roadmap. Physical gate length ( $L_{gate}$ )  |

| and power supply voltage (V <sub>DD</sub> )121                                                 |

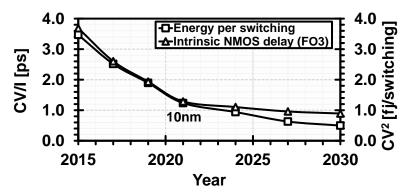

| Fig. 7.7. 2015 ITRS logic core device technology roadmap. Intrinsic NMOS delay                 |

| $(CV/I)$ and energy per switching operation $(CV^2)$ 122                                       |

| Fig. 7. 8. Four-times interleaved RDAC (4I-RDAC)123                                            |

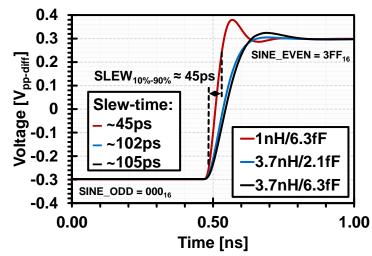

| Fig. 7. 9. Simulated settling times. RDAC unit parasitic capacitance $\approx 6.3 \mathrm{fF}$ |

| $(3.3 \times 12.43 \mu m^2)$ (3200 $\Omega$ ) and $\approx 2.1$ fF (1.65×6.215 $\mu m^2$ ) (3200 $\Omega$ ). Bonding wire |

|---------------------------------------------------------------------------------------------------------------------------|

| parasitic resistance/inductance $\approx 0.37 \Omega/3.7 nH$ and $\approx 0.1 \Omega/1 nH$ (1mm). No                      |

| power supply noise124                                                                                                     |

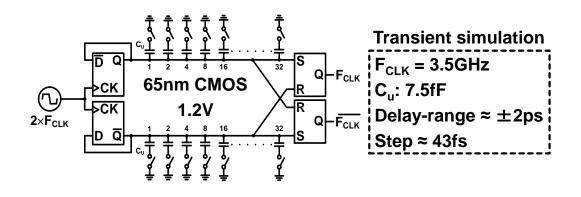

| Fig. 7. 10. Duty-cycle calibration technique [74]125                                                                      |

| Fig. 7.11. Complementary dual-phase PAC block based on SoP terms and employing the                                        |

| sine-phase difference algorithm                                                                                           |

## LIST OF TABLES

| Table 1-1: DDFS architectures and technologies.                             | 4     |

|-----------------------------------------------------------------------------|-------|

| Table 1-2: FMCW radar architectures.                                        | 15    |

| Table 1-3: Target DDFS performance.                                         | 20    |

| Table 2-1: Comparison of sequencing elements                                | 25    |

| Table 2-2: Comparison of sequencing elements                                |       |

| Table 3-1: Static timing, power and area analysis results                   | 50    |

| Table 3-2: Performance benchmark                                            | 55    |

| Table 4-1: Sampling errors caused by duty cycle distortions                 | 65    |

| Table 5-1: 16 FCW pre-stored values                                         | 76    |

| Table 6-1: Experimental results                                             | 92    |

| Table 6-2: Performance comparison                                           | 95    |

| Table 6-3: Performance comparison                                           | 104   |

| Table 6-4: Performance comparison with recently published RF-DACs           | 104   |

| Table 6-5: Performance comparison                                           | 113   |

| Table 6-6: Main features of the implemented complete-DDFS-solutions         | 115   |

| Table 7-1: Summary of the techniques composing the proposed design approact | ch117 |

| Table 7-2: Target vs. achieved DDFS performance                             | 119   |

| Table 7-3: Benefits and drawbacks of technology scaling                     | 122   |

| Table 7-4: Future development trends and techniques                         | 126   |

## CHAPTER 1:

### TRENDS AND LIMITATIONS OF THE DIRECT DIGITAL FREQUENCY SYNTHESIS TECHNOLOGY

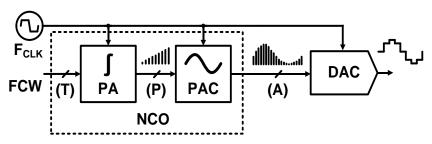

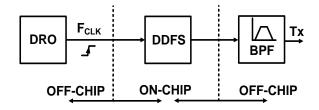

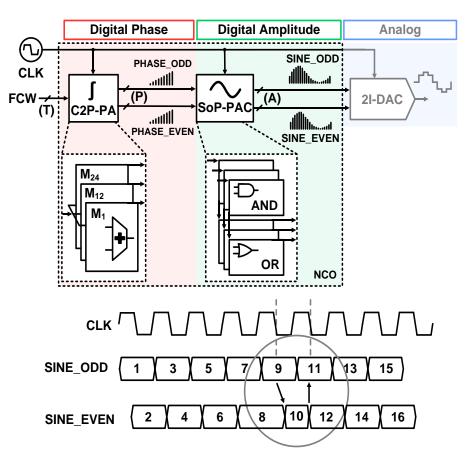

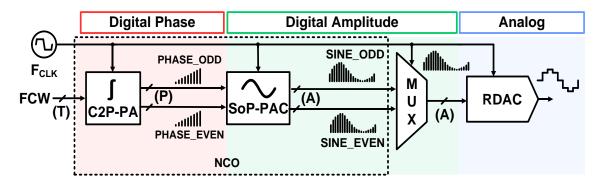

The concept of direct digital frequency synthesis was first introduced by J. Tierney in 1971 [1]. It can be defined as a digital signal processing (DSP) technique intended for representing a digital pattern in the analog domain based on a fixed clock period (frequency). The standard direct digital frequency synthesizer (DDFS) is a mixed signal device that generates a sinusoidal waveform at its output [1]. The phase step information contained in the frequency control word (FCW) is integrated by a phase accumulator (PA) and transformed into sinusoidal amplitude samples by a phase to amplitude converter (PAC). The digital unit conformed by concatenating the PA and the PAC blocks is also commonly identified in the literature as a numerically controlled oscillator (NCO). The digital representation of the sinusoidal waveform is transformed to the analog domain by using a linear digital to analog converter (DAC). This conventional architecture is often called digital-mapping DDFS (DM-DDFS) and its block diagram is represented in Fig. 1.1. The integration of a DAC and an NCO core in a single chip is frequently known as a complete-DDFS-solution.

Fig. 1.1. Conventional DM-DDFS architecture.

Where:

- *T*: Tuning word length.

- *P*: Phase word length.

- *A*: Amplitude word length.

Among others, four fundamental equations can be used to characterize the DDFS performance. The relationship between the FCW, the system clock frequency, and the tuning word length forms the basic tuning equation for conventional DDFS [2]:

$$F_{OUT} = \frac{FCW \cdot F_{CLK}}{2^{\mathrm{T}}}$$

(1.1)

Where:

- $F_{OUT}$ : DDFS output frequency.

- *F*<sub>CLK</sub>: System clock frequency.

A baseline study given in [3] has demonstrated how the magnitude of the phase truncation spurs has an upper bound that is determined by the number of bits in the phase word.

$$SFDR \approx 6.02P \, dBc \tag{1.2}$$

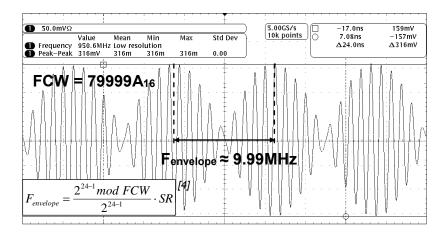

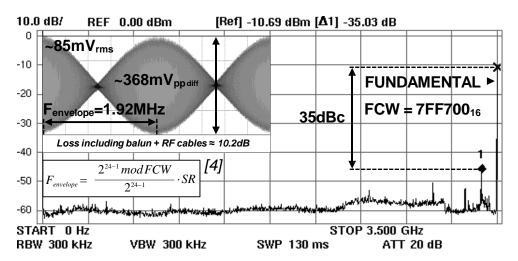

Additionally, the amplitude of the DDFS output will be also distorted as a result of the periodical overflow in the phase accumulator circuit. This behavior will create a "rolling" amplitude value at the output of the PAC block. The effect on the analog output is similar to the one observed in an amplitude modulated carrier. The frequency of the modulating signal can be determined as [4]:

$$F_{envelope} = \frac{2^{T-1} \mod FCW}{2^{T-1}} \cdot SR \tag{1.3}$$

Where:

- $F_{envelope}$ : frequency of the modulating signal.

- *SR*: sampling rate.

The numerical analysis disclosed in [5] leads to a theoretical limit of the signal to noise ratio (SNR) determined by the amplitude word length as (DC to SR/2):

$$SNR = 6.02A + 1.76 \, dB$$

(1.4)

The overall system performance depends on both the DDFS and the DAC characteristics. The maximum operating frequency, area, and power consumption are typically limited by the digital components of the DDFS. On the other hand, dynamic performance is mainly determined by the DAC, providing that low phase truncation

spurious-free dynamic range (SFDR) and proper timing are guaranteed in the DDFS core.

#### 1.1 Overview of high-speed DDFS architectures

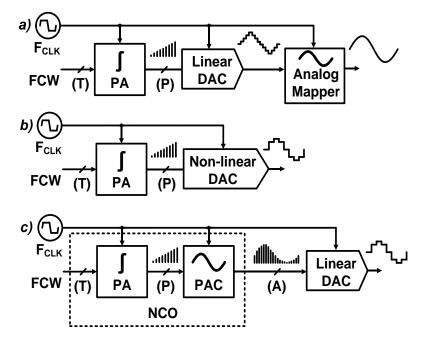

Multiple high-speed DDFS architectures have been published since the idea was first introduced by Tierney et al. in 1971 [1]. These topologies can be categorized into three groups according to the way the phase to amplitude conversion is implemented (Fig. 1.2). In all cases, the first block is a phase accumulator unit that integrates the FCW value to generate a phase ramp digital signal. In the analog mapping architecture (AM-DDFS), the phase to amplitude conversion is performed by using a linear DAC and an analog mapper circuit. The dependency on process, voltage, and temperature (PVT) variations of the analog mapper circuit limits the accuracy of this method [6]. The second approach employs a sine-weighted non-linear DAC (NLD-DDFS). The complexity of the sine-weighted DAC is higher than a linear one and its design becomes challenging when requiring higher amplitude resolution ( $\geq 12$  bits) [6]. Operation speeds up to 32GS/s have been reported in radar applications implementing these two methods in compound semiconductor technologies [7]. It should be noticed that when using the previously described architectures the phase to amplitude conversion is implemented in the analog domain. Consequently, amplitude modulation (AM) can't be performed in the digital domain [8].

Fig. 1.2. High-speed DDFS architectures. a) AM-DDFS. b) NLD-DDFS. c) DM-DDFS.

The DM-DDFS demands to pre-store the sinusoid digital values in a PAC block and typically exhibits a slow operation speed. The highest sampling rate reported in CMOS technology is only 2GS/s [9]. However, this is a robust digital intensive method that can benefit from the increasing integration density along with the transistor gate length scaling. Also, frequency, phase, and amplitude modulations can be implemented in the digital domain [8]. Table 1-1 summarizes some of the features of these architectures and relates them with the characteristics of the most suitable technologies in every case. The AM-DDFS and NLD-DDFS architectures feature a low/medium logic density and can take advantage of the higher carrier mobility in the compound semiconductor materials to boost the performance of the analog sections. The main drawbacks when employing these technologies are an increased power consumption and cost when compared with CMOS technology. On the other hand, the CMOS technology can be combined with the digitally intensive DM-DDFS architecture in order to reduce the power consumption and costs in mass productions.

| Architecture | Features                              | Preferred technology                                                                                                                                       |  |  |  |

|--------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AM DDES      | Low logic density                     |                                                                                                                                                            |  |  |  |

| AM-DDFS      | Analog centric                        | <b>SiGe, InP:</b><br>+ $f_T/f_{MAX} = 406$ GHz/423GHz in InP [8]                                                                                           |  |  |  |

|              | Medium logic<br>density               | <ul> <li>+ Better <i>1/f</i> noise [10]</li> <li>- Higher power consumption</li> <li>- Low integration density</li> </ul>                                  |  |  |  |

| NLD-DDFS     | Analog centric                        | - Higher cost                                                                                                                                              |  |  |  |

|              | Digital centric<br>High logic density | <b>CMOS:</b><br>- $f_T/f_{MAX} \approx 160$ GHz/200GHz in 65nm CMOS [11]                                                                                   |  |  |  |

| DM-DDFS      | Reduced analog sections               | <ul> <li>Larger <i>1/f</i> noise [10]</li> <li>Lower power consumption</li> <li>Higher integration density</li> <li>Low cost in mass production</li> </ul> |  |  |  |

TABLE 1-1: DDFS ARCHITECTURES AND TECHNOLOGIES.

Lower  $f_T f_{max}$  and larger 1/f noise are among the fundamental limitations when compared with SiGe or InP technologies. For that reason, analog sections with reduced complexity and digital compensation techniques should be adopted [10].

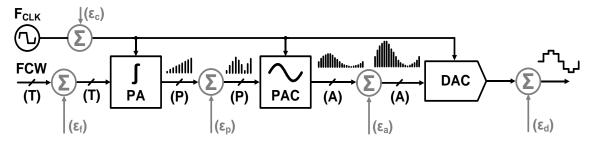

### 1.2 Non-idealities in DM-DDFS solutions

The general model employed to describe the non-idealities in a DM-DDFS can be represented as in Fig. 1.3 [2]. Except in the case of  $\varepsilon_f$ , these deviations from the ideal model in Fig. 1.2 c) will translate into phase noise and spur contents in the frequency domain. The quantization error inherent to the discrete approximation of the sampling step by a digital *FCW* will result in a fixed offset in the carrier frequency. Previous works have described in detail the effects of these distortions in the synthesized signal [12]-[15]. However, this background is relevant to the analysis of the simulation and measurement results and it will be briefly introduced in the following subsections.

Fig. 1.3. Model of a non-ideal DM-DDFS.

Where:

- $\mathcal{E}_c$ : Clock noise.

- $\mathcal{E}_f$ : Frequency deviation.

- $\mathcal{E}_p$ : Phase-truncation error.

- $\mathcal{E}_a$ : Amplitude quantization error.

- $\mathcal{E}_d$ : Digital to analog conversion error.

#### 1.2.1 Clock noise

Low phase noise can be achieved because the DDFS acts as a frequency divider

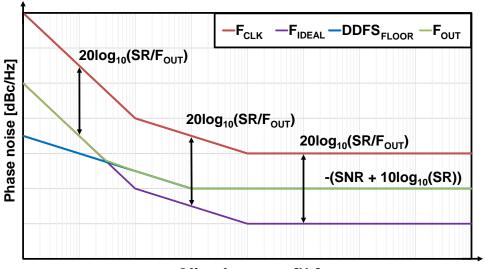

increasing the integration period of the edge jitter [12]. The relationship between the absolute phase noise at the input and output ports follows (1.5) [13]. This theoretical approximation has been confirmed by measurement of different DDFS devices in [12].

$$PN_{improvement} = 20\log_{10}\left(\frac{SR}{F_{OUT}}\right) [dB]$$

(1.5)

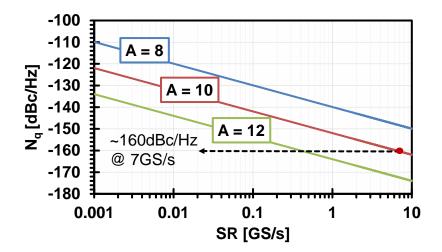

The close-in phase noise is limited by the clock source characteristics [12]. Any noise or spurs in the reference signal will be typically reflected in the phase noise characteristics at the DDFS output. The described behavior is represented in Fig. 1.4. It has been generally accepted as a rough model for the phase noise evaluation in DDFS systems [14]. The noise floor of the DDFS circuit will mask the clock contribution at some point and confine this improvement [14]. The expected noise floor of three DDFS having different amplitude word lengths was modeled across different clock frequencies and is represented in Fig. 1.5. It should be noticed that a quantization noise density of about -160dBc/Hz is expected when A = 10 and the system runs at 7GS/s. The quantization noise floor of the DDFS ( $N_q$ ) was approximated in [2] as:

$$N_{a} = -(SNR + 10\log_{10}(SR)) \text{ [dBc/Hz]}$$

(1.6)

**Offset frequency [Hz]**

Fig. 1.4. DDFS phase noise model.

Fig. 1.5. DDFS quantization noise floor.

### 1.2.2 Phase-truncation errors

As previously mentioned, the phase truncation errors will create a periodic distortion in the output of the PA block that generates spurious contents in the synthesizer output [15]. The maximum theoretical value can be determined by employing (1.2). It should be noticed that this errors can be reduced by increasing the number of bits addressing the PAC block. However, this will also increase the complexity of the phase to amplitude converter circuit. Conventionally, this spur lines are masked by the noise floor of the integrated DAC and do not define the overall wideband SFDR (W-SFDR) performance. As an example, when using a 14x10-bits PAC block, the SFDR degradation due to the truncation errors will have a theoretical maximum value of 84.28dBc (1.2). On the other hand, a high-speed 10-bits DAC will typically exhibit an SFDR performance poorer than the worst case spur due to the phase truncation effect.

### 1.2.3 Amplitude quantization errors

A periodic and additive distortion will result from the finite resolution that is employed to represent the sine waveform information in the digital domain. Similar to the phase truncation case, this errors can be mitigated by increasing the amplitude resolution of the employed PAC and DAC. However, this will inevitably lead to a growth in the area and power consumption. The magnitude of the generated spurs will depend on the numerical period of the output sequence [15]. In case the repetition ratio of the quantization error is relatively long when compared with the output signal period, the spur will be finely spaced approaching a white noise distribution [15]. A different scenario occurs when the quantization errors are more correlated with the output signal due to the reduction of the sine waveform period. In that case, it could be possible to have no amplitude quantization errors at all (the processed samples exactly matches the stored values with no quantization errors) or spurious lines having an estimated carrier to spur ratio (C/S) according to (1.7) [15] (assuming maximum quantization error in every sample and all the energy concentrated in one spur):

$$\frac{C}{S} = -3.01 + 6.02A \ [dBc] \tag{1.7}$$

Where:

• *A*: Number of bits at the PAC output.

According to this analysis, the expected worst case spur due to the correlated amplitude quantization errors should be below 57.19dBc when employing a 10-bits DAC.

### 1.2.4 Digital to analog conversion errors

The static and dynamic performance of the integrated DAC will ultimately define the spectral purity of the generated carrier. The mismatch between the elements employed as references for the digital to amplitude conversion can generate non-linear distortions that will affect the SFDR characteristics. However, in high-speed applications, the determinant factor is typically the dynamic performance. The artifacts resulting from incomplete settling times, code-dependent switching activity, induced power supply noise, clock feedthrough, imperfect switching time, output or input impedance modulation effects and other anomalies are typically stronger than those having a static nature.

### 1.3 State of the art

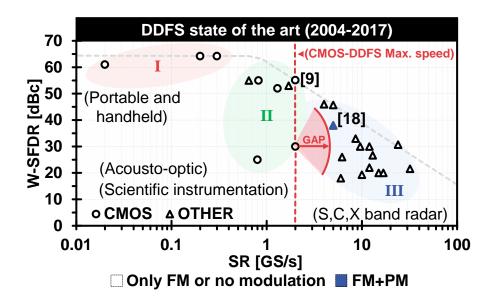

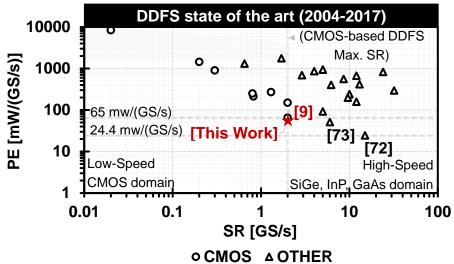

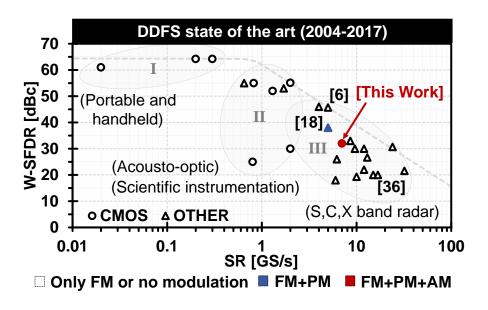

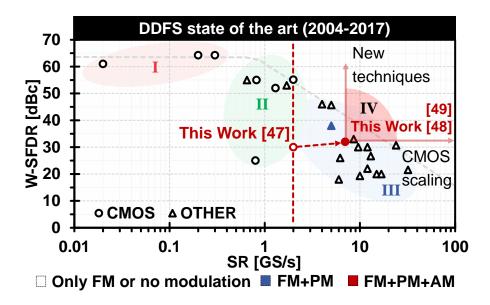

In Fig. 1.6 a selection of the best performance complete-DDFS-solutions reported since 2004 up to date is represented. Three main areas can be highlighted among the most widespread applications: regions (I), (II) and (III). The first one is defined by low-speed and low-power devices with a high SFDR. These features are increasingly demanded by portable and handled applications such as the baseband processing in Bluetooth transceivers [16]. Medium to high resolution (10 to 16 bits) digital-mapping direct DM-DDFSs are frequently employed in this group (the phase to amplitude conversion is performed in the digital domain).

Fig. 1.6. Complete-DDFS-solutions performance.

Since the clock frequency is relatively low, the penalty in energy consumption is less restrictive. In region (II), the most commonly used architectures are medium amplitude resolution (9 to 12 bits) DM-DDFS topologies and NLD-DDFSs. Fine frequency tuning resolution and high integration density can be achieved when using these solutions. These advantages are fully exploited in applications like acousto-optic radio frequency (RF) drivers [17] and scientific instrumentation. However, with clock frequencies up to about 2GHz, these synthesizers can barely cover the very high frequency (VHF) and ultra high frequency (UHF) bands.

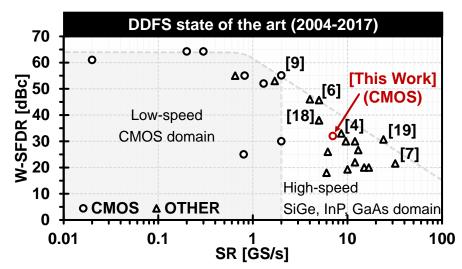

Continuously motivated by the advance in the compound semiconductor manufacturing process (reaching a  $f_T f_{max}$  of more than 300GHz/300GHz [4], [7]), the high-speed solutions have been exclusively dominated by these technologies. Low-resolution (5 to 8 bits) AM-DDFSs [6] or NLD-DDFS architectures [4], [7], [18] are commonly employed in the region (III). In both cases, the phase to amplitude conversion is implemented in the analog domain. Radar and frequency exploration systems operating in the S, C, and X bands require high output frequency, fine frequency resolution, fast channel switching and versatile frequency and phase modulation capabilities [18]. This performance can be achieved by implementing DDFS architectures in indium phosphide (InP) double heterojunction bipolar transistor (DHBT)) [7], [19] or silicon germanium (SiGe) technologies [4], [6], [18]. However, the applicability of these solutions is limited by the higher fabrication costs and more difficult access to foundry services. Additionally, amplitude modulation can't be performed in the digital domain when using these architectures. Only one design in

region III has reported frequency and phase modulations [18]. As a consequence, these approaches has been scarcely used in other application areas.

Although silicon complementary metal oxide semiconductor (CMOS) has become a mature and cost-effective technology, DDFS applications have been limited to regions I and II. The highest sampling rate (*SR*) among on-silicon CMOS-based DDFSs is only 2GS/s [9]. Due to these performance limitations, CMOS-based DDFS applications have been almost exclusively restricted to the VHF and UHF bands as defined by the Institute of Electrical and Electronics Engineers (IEEE) [20]. As a result, a performance gap can be observed between the state of the art of CMOS-based DDFSs and those devices implemented in compound semiconductor technology (Fig. 1.6).

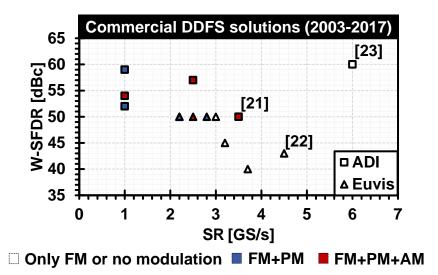

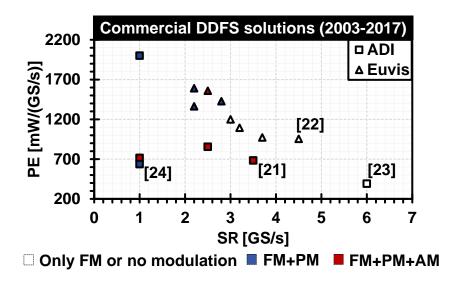

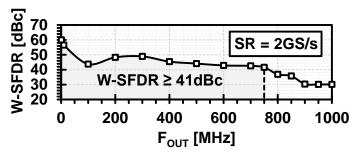

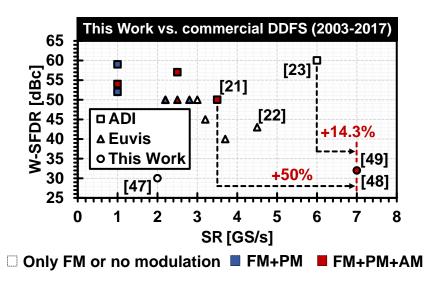

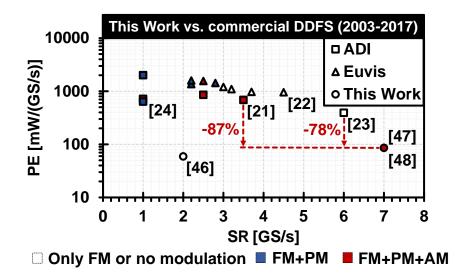

Several commercial DDFS solutions are currently available [21]-[24]. The maximum supported sampling rate among these devices is 6GS/s [23] (Fig. 1.7). Also, the best-reported power efficiency among these commercially available chips is about 390mW/(GS/s) [23]. The power consumption of the solutions operating in excess of 2GS/s in Fig. 1.8 is above 1W. It can be also noticed from Fig. 1.7 that several solutions integrate frequency, phase and amplitude modulation capabilities. However, the maximum sampling rate among this group is only 3.5GS/s [21]. This fact limits its practical application to systems operating up to about 1.4GHz (40% of the *SR*).

Fig. 1.7. W-SFDR performance of commercially available complete-DDFS-solutions.

Fig. 1.8. PE performance of commercially available complete-DDFS-solutions.

### 1.4 DDFS applications in radar technology

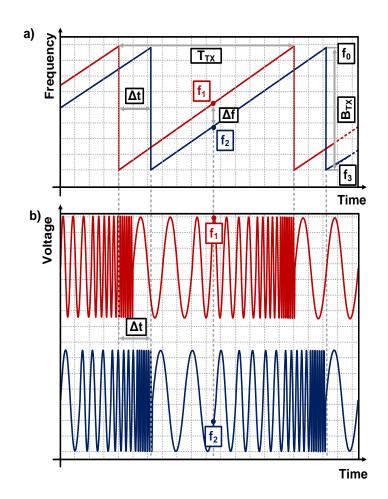

The linear frequency modulation (LFM) has been widely employed in frequency modulated continuous wave (FMCW) radars for determination of the actual range to a target [25]. This technique consists of generating a chirp signal and take the frequency difference between the transmitted and received waves after the downconversion [25] (Fig. 1.9). The range resolution ( $R_{RES}$ ) of the FMCW radar has been defined as [25]:

$$R_{RES} = \frac{c}{2B_{TX}} \tag{1.8}$$

Where:

- c: Speed of light.

- *B<sub>TX</sub>*: Bandwidth of the transmitted chirp.

The  $R_{RES}$  can be reduced by increasing the  $B_{TX}$ , which, at the same time, can be extended by spreading the frequency deviation of the generated chirp signal ( $f_3 - f_0$  in Fig. 1.9). Since the range information is obtained from this frequency difference between the transmitted and received chirps ( $\Delta f$ ), the linearity of the generated frequency modulation is of primary concern [25].

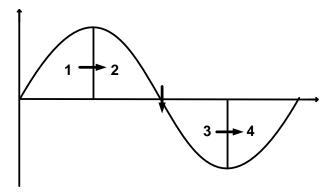

Fig. 1.9. Generated and received chirp signals. a) Frequency domain. b) Time domain.

Where:

- $\Delta f$ : Frequency difference between the transmitted and received chirps  $(f_2 f_1)$ .

- $\Delta t$ : Time difference between the transmitted and received chirps.

- $T_{TX}$ : Chirp length.

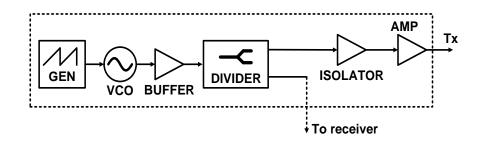

Different FMCW radar transmitters have been proposed [25]-[30], all of them having its own advantages and disadvantages. Topologies based on voltage controlled oscillators (VCO) were introduced in [26]-[28] (Fig. 1.10). Difficulties in controlling the gain of the VCO circuit typically limits the linearity of this approach. Process, voltage and temperature variations will also affect the performance of this circuit [25]. The frequency resolution is mainly determined by the VCO tuning sensitivity and the accuracy of the control voltage generator. The settling time is limited by the response time of the VCO (typically in the ns range).

Fig. 1.10. VCO-based FMCW radar transmitter.

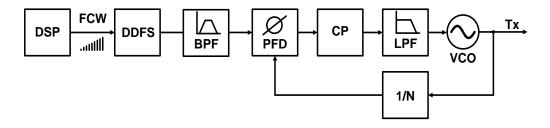

A second approach consists on implementing a hybrid DDFS-PLL system in which the DDFS core generates the chirp information for the frequency multiplication in the phase locked loop (PLL) [29], [30] (Fig. 1.11). A more linear frequency sweep and better immunity to PVT variations can be achieved by using this topology (locked to the accurate DDFS output) [30]. However, its inherent loop delay, limited frequency resolution (the DDFS resolution is multiplied by N in the PLL loop), and discontinuous-phase switching will translate in challenges when targeting a fast and wideband linear chirp signal [31]. Additionally, the use of a PLL will negatively impact the phase noise performance [14]. Another possible solution is to make use of a high-speed radio-frequency DAC (RF-DAC) [32] dynamically controlled by an external digital signal processing unit implemented in a field-programmable gate array (FPGA) device (Fig. 1.12).

Fig. 1.11. DDFS-PLL hybrid FMCW radar transmitter.

Where:

- *BPF*: Band-pass filter.

- *PFD:* Phase frequency detector.

- *CP:* Charge pump.

- *LPF:* Low-pass filter.

- *1/N:* Feedback divider.

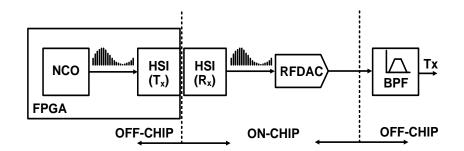

Fig. 1.12. FPGA+RF-DAC based FMCW radar transmitter.

Although this is a feed-forward structure that does not suffer from any delays associated with feedback loops, the power consumption is typically higher compared with other solutions. The dissipated energy is increased as a result of the high-speed interfaces (HSI) required to control the RF-DAC [33]. This system can be also understood as a discrete DDFS solution (with an increased cost in terms of the bill of materials and printed circuit board (PCB) complexity). Also, as demonstrated in [34], digital circuits implemented in FPGAs devices consume approximately 35 times larger area, 14 times more dynamic power and have between 3.4 to 4.6 times slower performance compared with ASIC implementations in equivalent technologies.

All programmable RF-sampling solutions have been recently reported in 16nm FinFET technology [35]. Power savings can be achieved when removing the need for high-speed interfaces by integrating an RF-DAC core with an FPGA fabric in a system on chip (SoC) solution [35]. However, this programmable structure still suffers from a slower operation speed and higher power consumption due to the general purpose logic required by the FPGA fabric [34]. Finally, high-speed complete-DDFS-solutions can be employed in order to accurately generate linear and wideband frequency chirps [23]. Furthermore, the DDFS reference can be driven by a low phase noise dielectric resonator oscillator (DRO) (Fig. 1.13), resulting in a feed-forward, PLL free, architecture [36]. The use of a direct digital frequency synthesizer offers a highly linear solution. However the maximum  $B_{TX}$ , and consequently, the minimum  $R_{RES}$ , is limited by the sampling rate of the DDFS [31]. The main benefits and drawbacks of the described FMCW transmitter architectures are summarized in Table 1-2. It should be noticed how the combination of a DRO and a complete-DDFS-solution can result in a system with fine frequency resolution, high linearity, fast and continuous-phase switching and excellent phase noise. Also, since this is a digitally intensive architecture, it is less affected by the aging and thermal drift of the components [15]. Achieving a high throughput while keeping a competitive power efficiency and SFDR performance represents the main challenges when integrating this mixed-signal system.

Fig. 1.13. DRO+DDFS based FMCW radar transmitter.

| Architecture   | Frequency resolution | Linearity | Switching<br>time | Phase<br>noise | PVT<br>variations/aging | Power<br>consumption | Solution<br>size/footprint |

|----------------|----------------------|-----------|-------------------|----------------|-------------------------|----------------------|----------------------------|

| VCO            | Medium               | Low       | Medium            | High           | High                    | Low                  | Small                      |

| DDFS<br>PLL    | Low                  | Medium    | Slow              | Medium         | Medium                  | Low                  | Medium                     |

| FPGA<br>RF-DAC | High                 | High      | Fast              | Low            | Low                     | High                 | Large                      |

| DRO<br>DDFS    | High                 | High      | Fast              | Low            | Low                     | Medium               | Medium                     |

TABLE 1-2: FMCW RADAR ARCHITECTURES.

### 1.5 Future evolution of DDFS applications

#### 1.5.1 Radar sensor for unmanned systems.

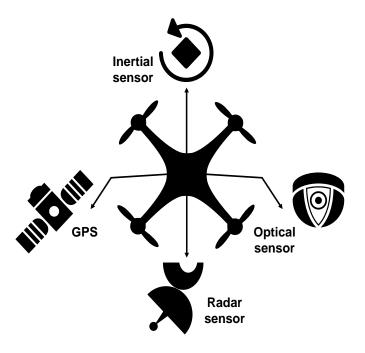

The use of surface and aerial unmanned systems (US) in civilian applications has an enormous growth potential in the near future. An increasing number of applications have been described [37]. These range from delivery services, industrial robots, and search and rescue missions to unmanned vehicles for agriculture and remote site exploration. It is also expected that the unmanned vehicles traffic will substantially grow in the upcoming years [37]. As a consequence, safety and security issues have been raised when evaluating possible interactions of the USs with conventional manned vehicles. These circumstances will demand the development of new onboard and ground-based sense-and-avoid systems (SAA) as well as traffic monitoring schemes. Among other technologies, such as optical systems, global positioning system (GPS) receivers, and inertial sensors, the radar technology should play an important role in the development of the next generation of collision avoidance systems [38]. One important advantage of the radar-based sensors compared with optical systems is that they are not affected by the ever-changing meteorological conditions. In the same way that radar technology has played an important role in large-scale air traffic control, it has the potential to be employed in miniaturized frequency exploration systems for unmanned vehicles. Although at present time the standards and requirements of this new radar generation for USs are still not available, some experimental results in the S-band (2.4GHz) [39], X-band (9.6GHz) [40], Ku-band [41] and Ka-band (35GHz) [42] have been reported. Among other technologies such as phase locked loops, the direct digital frequency synthesis technique has demonstrated to be a suitable solution for high-end radar applications. As illustrated in previous sessions, some of the DDFS benefits are unparalleled settling times (ns range) and tuning bandwidths, continuous-phase frequency switching with sub-Hertz resolution, low phase noise, and frequency/phase modulations in the digital domain. These characteristics have been exploited in conventional radar systems operating in the S, C and X bands [25]. However, there are a number of challenges that need to be addressed in order to fulfill the requirements of the new generation of radar sensors for miniaturized SAA applications.

First, these applications demand a reduction in both the power consumption and area of the high-speed DDFS solutions in order to be incorporated in multiple ground stations or onboard the unmanned vehicles/aircrafts. The direct digital frequency synthesis solutions are often power-hungry (several Watts) and occupy a large silicon area. These drawbacks become more critical in high-speed applications that are typically implemented in compound semiconductor technologies [4], [7]. Second, the DDFS system needs to be integrated into an increasingly digital environment. CMOS technology could potentially be employed in order to cover the required frequency bands while benefiting from its high integration density characteristics.

Fig. 1.14. Components of the onboard sense-and-avoid system.

Also, since the DDFS is a sampling system, spurious contents becomes an important issue to be taken into account.

### 1.5.2 Multi-band multi-standard polar modulator.

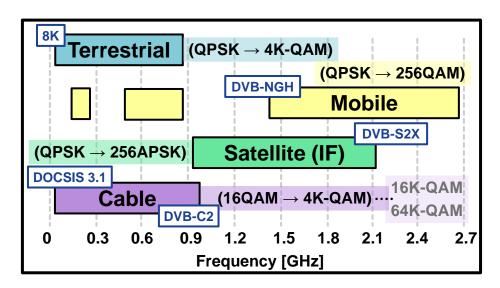

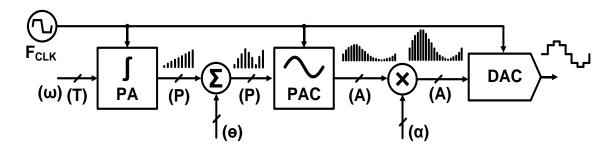

In the VHF, UHF and L bands the spectrum resources are very limited. The second generation of digital television (DTV) broadcasting systems is now calling for modulation orders up to 4K-QAM and beyond in order to support the increasing demand for higher data rates imposed by the new high-definition television standards [43]. Similarly, the cable standard DOCSIS 3.1 specifies 4K-QAM and includes 16K-QAM and 64K-QAM for future implementations (Fig. 1.15) [44]. Due to the increase in the modulation order, the minimum required C/N and transmitter modulation error rate (TxMER) are also more demanding [43]. The direct polar modulator (Fig. 1.16) instead of encoding the information into I and Q signals adopts the polar form in which the amplitude and phase of the constellation vectors are digitally generated by a direct digital frequency synthesizer [45]. For this reason, it can be considered I/Q mismatch free architecture. Low phase noise can be also achieved because the DDFS acts as a frequency divider increasing the integration period of the jitter [14]. Finally, all the modulations can be implemented in the digital domain, reducing the need for manual tuning or calibration due to the analog component aging or temperature drift. These are very attractive characteristics that could be potentially used in order to improve the TxMER in SoC transmitters. The direct polar modulator architecture resembles the block diagram depicted in Fig. 1.16.

Fig. 1.15. DTV broadcasting systems allocation and evolution.

Fig. 1.16. Direct polar modulator architecture.

$$DDFS_{out} = \alpha sin \left(2\pi \omega t + \theta\right) \tag{1.9}$$

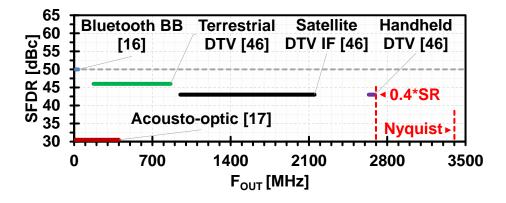

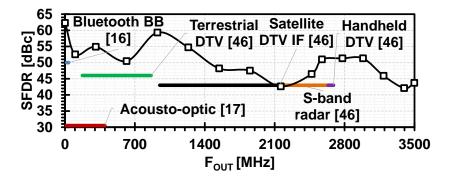

It should be noticed that the basic components are the same that can be found in a complete-DDFS-solution (Fig. 1.1). It additionally requires the digital modulation structures to be inserted into the main DDFS channel. These structures are an adder unit and a multiplier circuit employed to implement the digital phase and amplitude modulations respectively. The frequency, phase and amplitude of the output carrier can be digitally adjusted by dynamically changing the variables  $\omega$ ,  $\theta$  and  $\alpha$  in (1.9). However, practical implementations have been restricted by the speed of the digital blocks and the linearity and spurious performance of the DAC. A sampling rate of at least 6.8GS/s is required in order to cover all the broadcasting standards allocated in the VHF, UHF, L and S bands up to 2.7GHz (Fig. 1.17). A synthesizer with those characteristics could be also employed in other applications such as baseband processing in Bluetooth transceivers [16] and acousto-optic drivers [17]. At the same time, a spurious-free dynamic range from 43dBc to 50dBc (depending on the specific application) is required in order to guarantee a minimum level of interference among all the systems allocated in this crowded frequency bands [46] (Fig. 1.16).

Fig. 1.17. SFDR requirement of systems allocated in the VHF, UHF, L and S bands up to 2.7GHz.

The most important limitation resides in the fact that no DDFS solution with an  $SR \ge 6.8$ GS/s and supporting frequency, phase and amplitude modulations has been reported up to date (Fig. 1.6). The only design running at 5GS/s and demonstrating at least frequency and phase modulations was described in [18]. Commercial solutions supporting FM+PM+AM all together has been limited to sampling rates below 3.5GS/s (Fig. 1.7).

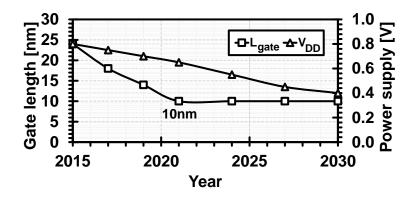

#### 1.6 Design challenges of high-speed DDFS solutions in CMOS technology

The main challenges when designing high-speed DDFS solutions in CMOS technology resides in how to increase the system throughput while keeping a competitive power efficiency (PE) and SFDR. The DDFS performance can potentially benefit from the increasing integration density along with CMOS technology scaling by reducing the complexity of the analog sections and employing digital compensation techniques. Shrinking of digital area and reduction of power consumption are still progressing along with the CMOS technology scaling. Furthermore, programmability and accurate predictability of digital technologies give us higher flexibility and robustness [10]. In line with previous statements, DM-DDFS is believed to be the most promising architecture for CMOS-based DDFS implementations. Since the DM-DDFS is a digitally intensive approach, the power consumption typically rises at higher sampling rates. Hence, techniques to reduce the power consumption while increasing the system throughput needs to be developed.

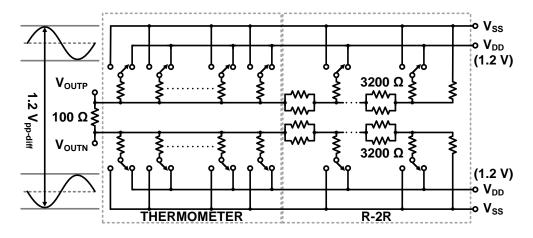

On the opposite side, the difficulty of low voltage operation of further scaled CMOS in analog circuits will be the most serious issue. This results in the saturation of performance and increase of cost [10]. Conventionally, the critical analog component in CMOS-based DM-DDFSs is the DAC. Resistive digital to analog converters are an interesting alternative to the conventional current-steering architectures employed in high-speed DDFSs. Unlike in current-steering based DACs, a rail-to-rail operation can be achieved even under the limited voltage headroom conditions imposed by the continuous CMOS technology scaling. However, mismatches among the resistor units will create non-linear distortions that should be compensated by employing calibration or dynamic element matching techniques.

The sampling nature of the DDFS systems will also generate spurs that fall within the first Nyquist zone. Digital compensation techniques should be implemented in order to improve both the static and dynamic performance of the CMOS-based synthesizers. The required SFDR for frequency exploration between 9kHz and 300GHz was defined by the International Telecommunication Union (ITU) according to 1.10 [46]. All radar system operating in the previously defined frequency band and with peak envelope power (*PEP*)  $\leq$  1W requires an SFDR  $\geq$  43dBc. It should be noticed that, to the best of the knowledge, no specific regulations about unwanted emissions in radar systems for small unmanned systems are currently available. The minimum SFDR requirements for broadcast, satellite and mobile television systems are also defined according to (1.10) in [46] and graphically represented in Fig. 1.17 (assuming PEP  $\leq$  1W).

$$SFDR = 43 + 10 \log PEP$$

, or 60 dBc, wichever is less stringent (1.10)

At present time, no device having at least frequency and phase modulation capabilities consumes less than 1W [18], [21]. At the same time, increasing the sampling rate in CMOS based digital designs leads to a proportional surge in the energy consumption. However, the power budget for SAA systems in unmanned vehicles is an increasingly limited resource. Hence, achieving a complete-DDFS-solution with FM+PM+AM capabilities and consuming less than 1W represents a challenge and can pave the way for future integration in onboard sensors.

The target DDFS performance can be summarized as in Table 1-3. A device with these characteristics could be potentially employed both as a radar sensor in SAA systems (up to S-band without using frequency multipliers) and as a multi-band multi-standard polar modulator covering frequencies up to 2.7GHz (40% of the *SR*).

| Technology | SR Mo  |     | dulations |     | Power              | SFDR  |

|------------|--------|-----|-----------|-----|--------------------|-------|

|            | [GS/s] | FM  | PM        | AM  | consumption<br>[W] | [dBc] |

| CMOS       | ≥6.8   | Yes | Yes       | Yes | ≤ 1                | ≥ 43  |

**TABLE 1-3:** TARGET DDFS PERFORMANCE.

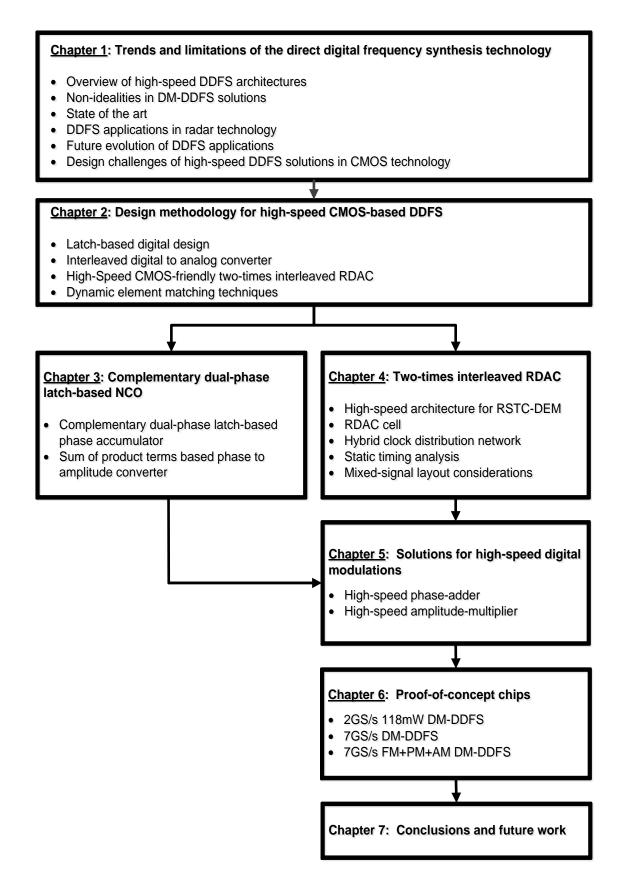

#### 1.7 Organization of the dissertation

This thesis is focused on the development and evaluation of high-speed solutions for CMOS-based DDFS devices. The manuscript is organized as follows:

In Chapter 1, the trends and limitations of the direct digital frequency synthesizer technology are introduced. Starting with an overview of the high-speed DDFS architectures, the state of the art of this technology is presented. A non-ideal model of a DM-DDFS system is also described. The current status and future evolution of DDFS

applications are also discussed. The main design challenges of high-speed DDFS implemented in CMOS technology are outlined as well. Chapter 2 is focused on the proposed design methodology aimed to maximize the throughput in CMOS-based DDFSs. Descriptions of the most common sequencing methods are included. Emphasis is made on the adopted latch-based digital design. The main techniques introduced in order to achieve the required throughput while keeping a competitive SFDR in the RDAC core are also discussed.

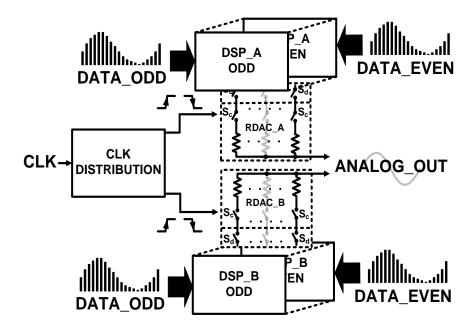

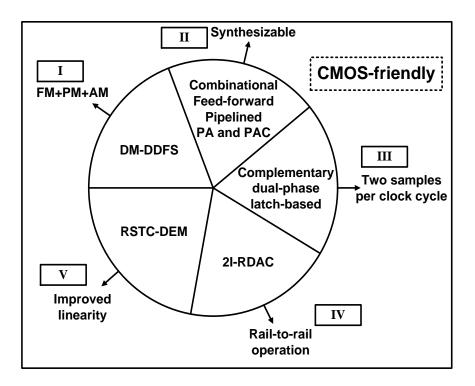

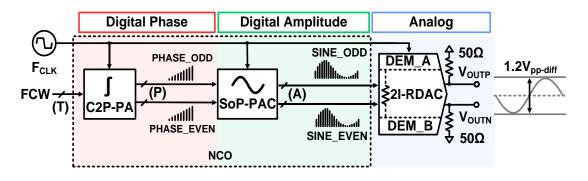

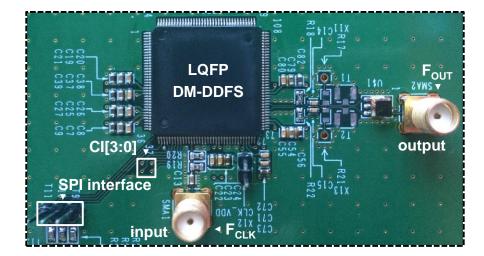

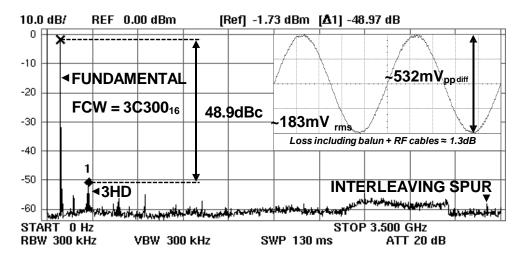

The circuit operation of the digital logic structures is examined in detail in Chapter 3. The description includes a 24-bits complementary dual-phase latch-based phase accumulator and also the proposed dual-phase sum of product terms based phase to amplitude converter. Similarly, in Chapter 4, the 10-bits two-times interleaved RDAC solution introduced in this work is presented. This converter features a high-speed architecture for random swapping thermometer coding dynamic element matching. All the circuit components are analyzed in detail, including the employed hybrid clock distribution network. Chapter 5 is dedicated to the solutions for high-speed digital modulations including a phase-adder and an amplitude-multiplier. Next, in Chapter 6, the proof-of-concept measurement results are analyzed. Three cases of study are presented: a 2GS/s 118mW digital-mapping direct digital frequency synthesizer in 65nm CMOS [47]; a 7GS/s direct digital frequency synthesizer with a two-times interleaved RDAC in 65nm CMOS [48]; and lastly, a high-speed DDFS MMIC with frequency, phase and amplitude modulations also implemented in 65nm CMOS technology [49]. The conclusions and future work are presented in Chapter 7.

Fig. 1.18. Organization of the dissertation.

## CHAPTER 2:

# DESIGN METHODOLOGY FOR HIGH-SPEED CMOS-BASED DM-DDFS

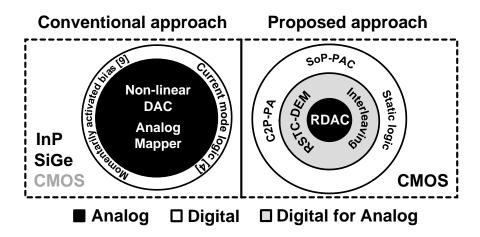

Conventionally, DDFS implementations in CMOS technology relies on approximation algorithms [50] or NLD-DDFS architectures [9] in order to increase the throughput. The first approach frequently leads to complex digital circuits that are difficult to speed up by employing parallelism or pipelining techniques. The second approach eliminates the need for a read-only memory (ROM) block (PAC) but increases the complexity of the analog sections (DAC). This imposes additional challenges when employing CMOS technology. Also, flip-flop based architectures have been often selected and almost no other sequencing methods have been explored. As a consequence, up to date, the highest sampling rate among on-silicon CMOS-based DDFSs is only 2GS/s [9]. Although DM-DDFS architectures have been reported in compound semiconductor technologies [19], [51], they are also limited either in power or speed Fig. 2.1. The designs in Fig. 2.1 employs pipelined phase accumulators and current-steering DACs.

|                                     | Digital Phase    | Digital Amplitude       | Analog              |  |

|-------------------------------------|------------------|-------------------------|---------------------|--|

| F <sub>cLK</sub><br>FC₩             | <b>F</b> A       |                         | DAC →               |  |

| [ <b>19] InP</b><br>24GS/s<br>19.8W | 12b<br>pipelined | ROM-based               | Current<br>Steering |  |

| <b>[51] SiGe</b><br>1.7GS/s<br>3W   | 32b<br>pipelined | Linear<br>approximation | Current<br>Steering |  |

Fig. 2.1. DM-DDFS implementations in compound semiconductor technologies.

A ROM-based implementation in InP achieves a 24GS/s record speed for a DM-DDFS [19]. However, the power consumption reaches 19.8W. By using a linear approximation method a SiGe implementation reports 3W [51]. Still, the circuit complexity limits the maximum speed to only 1.7GS/s.

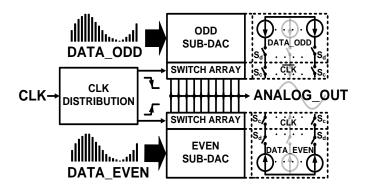

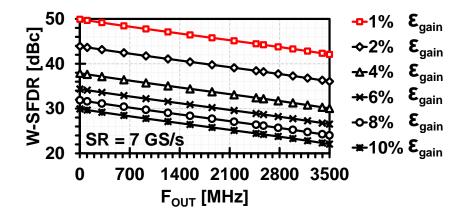

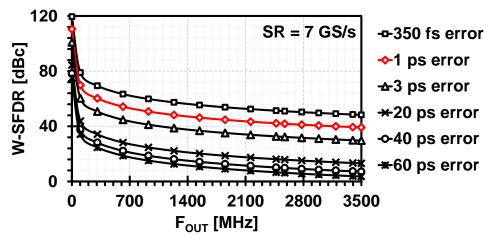

In this work, a different design approach is proposed. First, a complementary dual-phase latch-based DM-DDFS architecture is adopted. This method proves to be advantageous in terms of maximum throughput, power efficiency and yield. Also, the PAC block was generated by employing the sum of product (SoP) terms obtained from a 14×10-bits lookup table. The resulting architecture is a feed-forward digital circuit that can be easily speed up by using intensive pipelining in a complementary and parallel structure. Finally, instead of relying on current-steering data converters, an interleaved RDAC is introduced. Unlike in current-steering based DACs, a rail-to-rail operation can be achieved even under the limited voltage headroom conditions imposed by the continuous technology scaling. This is an important feature in terms of technology portability. The basics of these techniques will be discussed in this chapter. It serves as a preamble for the detailed circuit operation descriptions in Chapter 3.

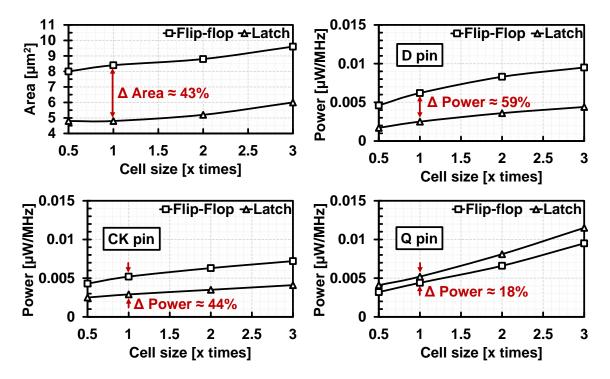

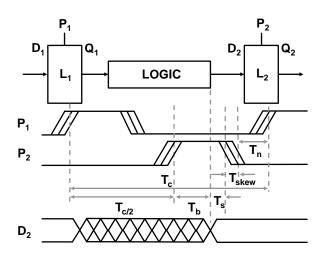

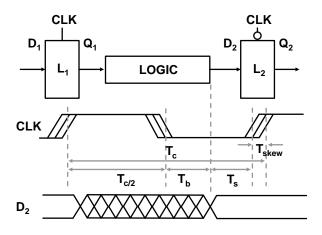

#### 2.1 Sequencing methods

Several factors need to be taken into account when adopting a sequencing method for high-performance digital designs. Among them, sequencing overhead, skew tolerance, power consumption, area, and simplicity are usually of primary concern. Flip-flops, pulsed latches, and transparent latches have different advantages and disadvantages that will impact the final quality of results [52]. By far, the most popular sequencing method is based on flip-flop devices. Although the timing relationships are quite simple, these systems usually underperform when compared with other approaches. Given its ease of use [52], flip-flops are a good option if, for a certain technology, the throughput or power efficiency requirements are not stringent. However, the ever-increasing demand for higher data rates is constantly reducing the design margins in the available technologies. For that reason, schemes that can push the system performance close to the technology limits are usually required. Transparent latches exhibit lower sequencing overhead and allow almost half a cycle of time borrowing which turns into higher throughputs [52]. Three alternatives are commonly employed: dual-phase nonoverlapping, dual-phase complementary latches and pulsed latches. The difference between the first two methods resides in the way the clock signal is distributed. The former case employs two different clock signals with nonoverlapping

phases to synchronize a pair of consecutive latch elements. In the second case, only one clock signal needs to be distributed and successive latches are enabled during different levels of the clock. Pulsed latches can be viewed as transparent latches with a narrow pulse. They are also capable of a small amount of time borrowing if the pulse is wider than the set-up time. Table 2-1 summarizes the timing characteristics of the previously described sequencing methods [52]:

| Sequencing method            | Timing overhead<br>(T <sub>c</sub> – T <sub>pd</sub> ) | Maximum borrowed time<br>(T <sub>b</sub> ) | Minimum-timing constraint<br>(T <sub>min</sub> ) |

|------------------------------|--------------------------------------------------------|--------------------------------------------|--------------------------------------------------|

| Dual-phase<br>nonoverlapping | $2T_{pdq}$                                             | $T_{c/2}$ - $(T_s + T_{skew} + T_n)$       | $T_h - T_{ccq} + (T_{skew} - T_n)$               |

| Dual-phase<br>complementary  | $2T_{pdq}$                                             | $T_{c/2}$ - $(T_s + T_{skew})$             | $T_h$ - $T_{ccq}$ + $T_{skew}$                   |

| Flip-flop                    | $T_{pcq} + T_s + T_{skew}$                             | 0                                          | $T_h - T_{ccq} + T_{skew}$                       |

| Pulsed latches               | $T_{pdq}$                                              | $T_{pw} - (T_s + T_{skew})$                | $T_h - T_{ccq} + (T_{skew} + T_{pw})$            |

TABLE 2-1: COMPARISON OF SEQUENCING ELEMENTS.

Where:

- $T_c$ : Clock period.

- $T_{c/2}$ : Half clock period.

- $T_b$ : Borrowed time.

- $T_s$ : Set-up time.

- $T_h$ : Hold time.

- $T_{skew}$ : Clock skew.

- *T<sub>n</sub>*: Nonoverlapping time.

- $T_{pw}$ : Pulse width.

- $T_{pdq}$ : D-to-Q propagation delay.

- $T_{pcq}$ : Clock-to-Q propagation delay.

- $T_{ccq}$ : Clock-to-Q contamination delay.

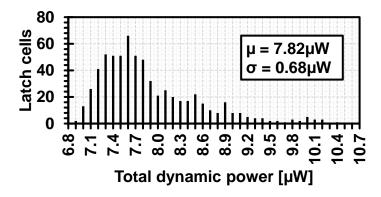

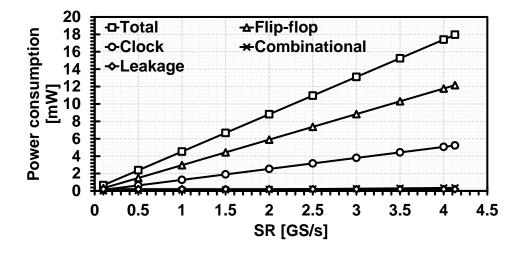

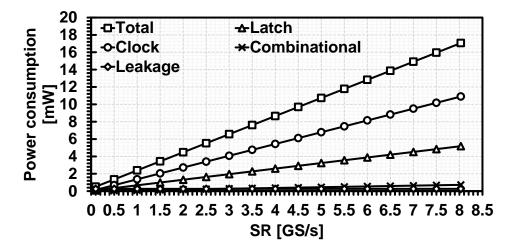

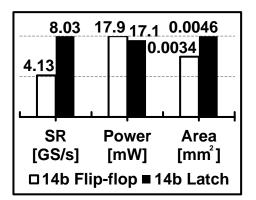

- $T_{pd}$ : Logic propagation delay.